Fairchild 9440

The Fairchild 9440 MICROFLAME, also known as the F9440 and μFLAME, was a 16-bit microprocessor introduced by Fairchild Semiconductor in 1977. The 9440 implemented the Data General Nova 2's instruction set in a single-chip 40-pin DIP. The name "MICROFLAME" was part of a wider branding exercise, "FIRE", which was a development software system.

An updated version, the 9445, was announced in 1978 but did not reach market until late 1981. By this time the 16-bit designs were being surpassed by 32-bit designs and hybrids like the Motorola 68000, and Fairchild began turning their attention to their own 32-bit Fairchild Clipper design. The underlying core of the 9445 was also used to implement the 9450, which used new microcode to implement the MIL-STD-1750A instruction set.

The 9440 and 9445 were subject to constant lawsuits from Data General (DG) that dragged on both companies. DG finally settled all ongoing litigation in September 1986 by paying Fairchild over $52 million. Fairchild was purchased and sold several times during this period, ending up at National Semiconductor in 1987. National ended production of the 9445, leaving several users in the lurch. A final version, the IDC9445, was introduced to fill this need.

The National Semiconductor IMP-16 and PACE were similar chip-based implementations inspired by the Nova, but did not draw the ire of DG. This is likely due to Fairchild having been DG's primary chip supplier.

History

Nova

The Data General NOVA was introduced in 1969, implemented using individual integrated circuits (ICs) mounted on a 15x15-inch printed circuit board. In order to lower design complexity, and thus board size and cost, the arithmetic logic unit (ALU) was only 4-bits wide, implemented using a single 74181 IC. This meant it required four machine cycles to complete a 16-bit instruction, but it also allowed the system to be much less expensive than competing minicomputers from Digital Equipment Corporation (DEC) or Hewlett-Packard. The NOVA was very successful, propelling DG into the second-place position behind DEC in the minicomputer market during the 1970s.[1]

In 1970, DG introduced the SuperNOVA, which featured a full 16-bit wide ALU using four 74181's in bit-slice fashion, and thus ran about four times as fast as the original NOVA. This was further boosted by other changes, including faster core memory and optional semiconductor memory, making the SuperNOVA the fastest mini for some time. This also meant there were two different central processing unit designs implementing the same underlying instruction set architecture (ISA). As development of both designs continued, the two were modified so the faster version could be dropped into existing machines originally running the lower-speed hardware. This led to the NOVA 2, 3 and 4 series.

microNOVA

Improving semiconductor fabrication processes, especially through the 1970s, put increasing pressure on the individual-IC CPU designs. Initially only 4-bit and then 8-bit CPUs could easily be manufactured on a single chip, but by the mid-1970s, 16-bit designs were appearing. In 1973, National Semiconductor introduced the IMP-16, which implemented a NOVA-like system in a set of only five IC's. The next year their PACE reduced that to a single IC. Several similar designs appeared during this period, including the Texas Instruments TMS 9900, which implemented their TI-990 minicomputer, and the Intersil 6100, a single-chip version of the PDP-8.

DG needed to respond to these systems, and began development of the microNOVA mN601, a single-chip design that implemented the NOVA 3 instruction set.[1] It also added hardware single-precision multiply and divide, formerly an optional add-on for NOVA systems. It was announced in early 1976, and sold to anyone who wanted one - they could be purchased as a single chip, a CPU card with support chips, or a complete packaged NOVA machine. The individual chips sold for $225, or $95 in lots of 100.[2] Later, however, DG stopped direct sales of the 601 in favor of selling complete systems.[1]

The mN601 was implemented using NMOS technology, and thus required four separate input voltages from the power supply.[1] It also lacked an internal clock, and required the system to provide a two-phase clock signal to drive it. It ran at fairly low speeds, normally using a 240 ns clock (~4.2 MHz), completing instructions in 2.4 to 10 µs.[3] This, along with limitations on the bus performance, meant the system performed about half as fast as an original Nova.[3]

Throughout the evolution of the Nova line, the systems had been built primarily using discrete ICs from Fairchild Semiconductor, a leader in IC design during the 1960s. This relationship ended with the microNOVA, which was fabbed at a new DG-owned factory in Sunnyvale, California.[2]

9440

For reasons that are not recorded in the historical record, Fairchild decided to produce their own single-chip implementation of the NOVA design, without Data General's approval. The courts had already decided that the instruction set of a CPU was not subject to copyright, and this had been tested several times by companies that implemented IBM mainframe compatible systems using different internal implementations. DG had also done nothing about the introduction of the IMP-16 and PACE, both similar to DG design.[4]

Fairchild had ample reason to believe a new implementation of the Nova would be legally OK. To their surprise, DG sued in 1977, not for design infringement, but claiming that Fairchild was enticing DG's customers to break their licensing agreements. These stipulated that DG software was only allowed to run on DG hardware. The next year, Fairchild counter-sued, claiming DG's licensing broke anti-competition laws.[3]

The 9440 was much more expensive than the mN601; the former sold for $395 in lots of 100, including the software package,[5] while the later was $95 for the same quantity. The combination of the higher prices and lawsuit made the 9440 a slow seller, and it was not picked up for second-source by any of Fairchild's normal partners.[4]

9445

An updated version, the 9445, was announced in 1978. Using a new 2-micron process, the 9445 implemented the NOVA 3 instruction set in microcode, added built-in hardware multiply and divide, and added addressing for up to 128 kWords. In contrast to the 9440, which ran about the same speed as an original NOVA, the 9554 was quite fast; Fairchild claimed it would run ten times faster than an actual NOVA 3.[4]

Production problems greatly delayed market introduction. This was one of the largest bipolar CPUs attempted to this point. The 9445 finally began deliveries in late 1981 at 16 MHz, and later improved to 20 and 24 MHz. By this time the first 32-bit microprocessors were coming to market, and all of the Nova-based machines were outdated.[4]

DG sued again, and eventually there were eleven lawsuits in progress. Schlumberger, originally an oil services company but looking to branch out, purchased Fairchild in 1979. This meant Fairchild was well capitalized and they continued to fight the lawsuits. In 1986, with the minicomputer market collapsing as newer IBM PC designs began to take over their market, DG decided to settle. In September 1986, DG agreed to pay Fairchild $52.5 million. By this time the NOVA line was no longer made, and interest in the 9445 was long dead.[4]

Schlumberger decided to exit the business, and in 1987 they sold Fairchild to National Semiconductor, who immediately ended production of the line.[4]

Description

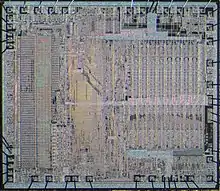

9440

In contrast to the NMOS mN601, Fairchild's 9440 design was fabbed using Fairchild's proprietary 3-micron bipolar transistor Isoplanar Integrated Injection Logic process, I3L. This was a transistor-transistor logic (TTL) system, so the resulting chip required only a single +5V power supply instead of the four-level supply of the mN601. The process also allowed it to run faster, up to 12 MHz; whereas the mN601 ran about half the speed of the original Nova, the 9440 ran about the speed of a Nova 1200. They also integrated the clock generator and oscillator, removing the need for additional external clock support, although it could read an external clock if one was provided. It shipped in the same 40-pin DIP as the mN601.[6]

Internally, the system was different than the NOVA 2; as the data sheet put it, "Though structurally different from the CPUs of the Data General NOVA line of minicomputers, the 9440 offers comparable performance and executes the same instruction set."[7] This was possible because the instruction set was in microcode,[8] allowing the CPU to (in theory) be of any design at all.

The μFLAME differed from the mN601 slightly in programming model, as its instruction set was based on the NOVA 2, not NOVA 3, and thus lacked the hardware stack that had been introduced on the 3. It also lacked the hardware multiply and divide of the mN601, although this could be added with the optional 9443 Special Function Unit. The 9441 Memory Control Unit (MCU) and 9442 I/O Control Unit rounded out the complete system. Unrelated to the 9440 specifically, Fairchild also sold suitable dynamic RAM chips (DRAM), the 4 kB 93481 and 16 kB 93483.[9]

There are two other major differences between the mN601 and 9440. While the 9440 included direct memory access (DMA) signals to indicate the start and end of a DMA process, when it received them it simply paused and released the system bus. It was up to the external hardware to actually move the data into memory.[3] In contrast, the NOVA performed an optional interrupt that allowed the processor itself to move data, jumping through an address in memory location 0001.[10] Additionally, the mN601 had an internal DRAM refresh system, which performed a refresh every 20,000 internal cycles. The 9440 lacked this internally, and left this to the 9441.[11]

Fairchild also offered a development suite for the system, the FIRE package.[6]

9445

The 9445, no longer referred to as a MICROFLAME, was a major advance on the 9440. One significant change was the move from 3-micron to 2-micron feature sizes, which allowed more gates to be constructed on the chip without affecting yield, and allowing the operating speeds to be increased to 24 MHz, double that of the 9440.[12]

The 9445 fully implemented the NOVA3 instruction set, adding the SP (stack pointer) and FP (frame pointer) registers to support the hardware stack. The 9445 also supported the NOVA3's new bank-switched memory system, which extended the address space from 32 kWord to 128. This change also required the addition of the NOVA3's three new addressing modes, for a total of eleven. It added the hardware-based 16-bit multiply and divide that had been left out of the 9440, eliminating the need for the 9443. On top, it added a suite of new opcodes to help with floating point math, which could operate on 8-, 16- or 32-bit data.[12] The ALU was expanded from 4-bits to a full 16-bit implementation, greatly improving overall performance.[13]

9450

Fairchild used the same underlying processor design of the 9445, with different microcode, to produce the 9450. This provided the MIL-STD-1750A instruction set instead of the Nova's. This reached the market in 1985, offering a built-in math processor, an optional external chip on most other 1750A implementations.[4]

References

Citations

- Osborne 1981, p. 4.1.

- mNOVA 1976, p. 4.

- Osborne 1981, p. 4.2.

- MicroFlame 2017.

- "9440". CPU Shack.

- 9440 1978, p. 1.

- 9440 1978, p. 2.

- 9440 1978, p. 3.

- 9440 1978, p. 10.

- Osborne 1981, p. 4.30.

- Osborne 1981, p. 4.4.

- 9445, p. 6.51.

- 9445, p. 6.52.

Bibliography

- "MicroNova Microcomputer Family" (PDF). Microcomputer Digest. July 1976.

- 9440 MICROFLAME (Technical report). Fairchild Semiconductor. 1978.

- Fairchild Microcomputers (PDF) (Technical report). Fairchild Semiconductor.

- Osborne 16-Bit Microprocessor Handbook (PDF). Osborne/McGraw-Hill. 1981.

- "When a Minicomputer becomes a Micro: the DGC microNOVA mN601 and 602". CPU Shack. 21 November 2014.

- "CPU of the Day: Fairchild F9445: The MicroFlame Flames Out". CPU Shack. 14 November 2017.