Intel 8253

The Intel 8253 and 8254 are Programmable Interval Timers (PITs), which perform timing and counting functions using three 16-bit counters.[1]

The 825x family was primarily designed for the Intel 8080/8085-processors, but later used in x86 compatible systems. The 825x chips or equivalent circuit embedded in a larger chip are found in all IBM PC compatibles, and the soviet computers like Vector 06C.

In PC compatibles, Timer Channel 0 is assigned to IRQ-0 (the highest priority hardware interrupt). Timer Channel 1 is assigned to DRAM refresh (at least in early models before the 80386). Timer Channel 2 is assigned to the PC speaker.

The Intel 82c54 (c for CMOS logic) variant handles up to 10 MHz clock signals.[1]

History

The 8253 is described in the 1980 Intel "Component Data Catalog" publication. The 8254, described as a superset of the 8253 with higher clock speed ratings, has a "preliminary" data sheet in the 1982 Intel "Component Data Catalog".

The 8254 is implemented in HMOS and has a "Read Back" command not available on the 8253, and permits reading and writing of the same counter to be interleaved.[2]

Modern PC compatibles, either when using SoC CPUs or southbridge typically implement full 8254 compatibility for backward compatibility and interoperability.[3] The Read Back command being a vital I/O feature for interoperability with multicore CPUs and GPUs.

Variants

There is military version of Intel M8253 with the temperature range of -55°C to +125°C which it also have ±10% 5V power tolerance.[4]

Features

The timer has three counters, numbered 0 to 2.[5] Each channel can be programmed to operate in one of six modes. Once programmed, the channels operate independently.[1]

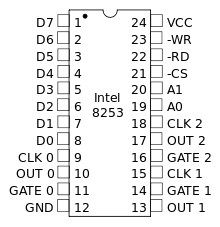

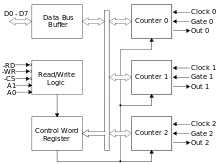

Each counter has two input pins – "CLK" (clock input) and "GATE" – and one pin, "OUT", for data output. The three counters are 16-bit down counters independent of each other, and can be easily read by the CPU.[6]

- Data bus buffer contains the logic to buffer the data bus between the microprocessor and the internal registers. It has 8 input pins, usually labelled as D7..D0, where D7 is the MSB.

- Read/write logic has 5 pins, which are listed below. The "X" denotes X is an active low signal.

- RD: read signal

- WR: write signal

- CS: chip select signal

- A0, A1: address lines

Operation mode of the PIT is changed by setting the above hardware signals. For example, to write to the Control Word Register, one needs to set CS=0, RD=1, WR=0, A1=A0=1.

- The control word register contains the programmed information which will be sent (by the microprocessor) to the device. It defines how each channel of the PIT logically works. Each access to these ports takes about 1 µs.

To initialize the counters, the microprocessor must write a control word (CW) in this register. This can be done by setting proper values for the pins of the Read/Write Logic block and then by sending the control word to the Data/Bus Buffer block.

The control word register contains 8 bits, labeled D7..D0 (D7 is the MSB). The decoding is somewhat complex. Most values set the parameters for one of the three counters:

- The most significant two bits (if not 11) select the counter register the command applies to.

- The next two bits (if not 00) select the format that will be used for subsequent read/write access to the counter register. This is commonly set to a mode where accesses alternate between the least-significant and most-significant bytes. One difference between the 8253 and 8254 is that the former had one internal bit which affected both reads and writes, so if the format was set to 2-byte, a read of the lsbyte would cause a following write to be directed to the msbyte. The 8254 used separate bits for reads and writes.

- The next three bits select the mode that the counter will operate in.

- The least significant bit selects whether the counter will operate in binary or BCD. (BCD counting almost never used and may not be implemented properly in emulators or southbridges.)

However, there are two other forms:

- Latch the count for a given timer. The next read will, rather than returning the counter value at the moment of the read, return the counter value at the moment of the latch command. After the read completes, later reads will return the current counter. When the latch command is used, the mode and BCD status are not changed.

- (8254 only) Latch the status and/or count for multiple timers. This allows multiple simultaneous latch commands using a bitmap. Also, the current channel configuration may be read back in addition to the count.

| Bit #/Name | Short Description | |||||||

|---|---|---|---|---|---|---|---|---|

| D7 SC1 |

D6 SC2 |

D5 RW1 |

D4 RW0 |

D3 M2 |

D2 M1 |

D1 M0 |

D0 BCD | |

| 0 | 0 | format | mode | BCD | Set mode of Counter 0 | |||

| 0 | 1 | format | mode | BCD | Set mode of Counter 1 | |||

| 1 | 0 | format | mode | BCD | Set mode of Counter 2 (at port 42h) | |||

| 1 | 1 | count | status | C2 | C1 | C0 | x | Read-back command (8254 only) |

| counter | 0 | 0 | — x — | Latch counter value. Next read of counter will read snapshot of value. | ||||

| counter | 0 | 1 | mode | BCD | Read/Write low byte of counter value only | |||

| counter | 1 | 0 | mode | BCD | Read/Write high byte of counter value only | |||

| counter | 1 | 1 | mode | BCD | 2×Read/2xWrite low byte then high byte of counter value | |||

| counter | format | 0 | 0 | 0 | BCD | Mode 0: Interrupt on Terminal Count | ||

| counter | format | 0 | 0 | 1 | BCD | Mode 1: Hardware Retriggerable One-Shot | ||

| counter | format | x | 1 | 0 | BCD | Mode 2: Rate Generator | ||

| counter | format | x | 1 | 1 | BCD | Mode 3: Square Wave | ||

| counter | format | 1 | 0 | 0 | BCD | Mode 4: Software Triggered Strobe | ||

| counter | format | 1 | 0 | 1 | BCD | Mode 5: Hardware Triggered Strobe (Retriggerable) | ||

| counter | format | mode | 0 | Counter is a 16-bit binary counter (0–65535) | ||||

| counter | format | mode | 1 | Counter is a 4-digit binary coded decimal counter (0–9999) | ||||

| 1 | 1 | count | status | C2 | C1 | C0 | x | Read-back command (8254 only) |

| 1 | 1 | 0 | 0 | C2 | C1 | C0 | x | Next read of selected counters will read back latched status, then count |

| 1 | 1 | 0 | 1 | C2 | C1 | C0 | x | Next read of selected counters will read back latched count |

| 1 | 1 | 1 | 0 | C2 | C1 | C0 | x | Next read of selected counters will read back latched status |

| 1 | 1 | 1 | 1 | C2 | C1 | C0 | x | Do nothing (latch nothing on any or all counters) |

| 1 | 1 | count | status | 0 | 0 | 0 | x | Do nothing (latch count and/or status on no counters) |

| 1 | 1 | count | status | 1 | C1 | C0 | x | Read-back command applies to counter 2 |

| 1 | 1 | count | status | C2 | 1 | C0 | x | Read-back command applies to counter 1 |

| 1 | 1 | count | status | C2 | C1 | 1 | x | Read-back command applies to counter 0 |

When setting the PIT, the microprocessor first sends a control message, then a count message to the PIT. The counting process will start after the PIT has received these messages, and, in some cases, if it detects the rising edge from the GATE input signal. Status byte format. Bit 7 allows software to monitor the current state of the OUT pin. Bit 6 indicates when the count can be read; when this bit is 1, the counting element has not yet been loaded and cannot be read back by the processor. Bits 5 through 0 are the same as the last bits written to the control register.

| Bit #/Name | Short Description | |||||||

|---|---|---|---|---|---|---|---|---|

| D7 Output Status |

D6 null count |

D5 RW1 |

D4 RW0 |

D3 M2 |

D2 M1 |

D1 M0 |

D0 BCD | |

| 0 | Out pin is 0 | |||||||

| 1 | Out pin is 1 | |||||||

| 0 | Counter can be read | |||||||

| 1 | The counter is being set | |||||||

| format | mode | BCD | Counter mode bits, as defined for the control word register | |||||

Operation modes

The D3, D2, and D1 bits of the control word set the operating mode of the timer. There are 6 modes in total; for modes 2 and 3, the D3 bit is ignored, so the missing modes 6 and 7 are aliases for modes 2 and 3.

All modes are sensitive to the GATE input, with GATE high causing normal operation, but the effects of GATE low depend on the mode:

- Modes 0 and 4: Counting is suspended while GATE is low, and resumed while GATE is high.

- Modes 1 and 5: The rising edge of GATE starts counting. GATE may go low without affecting counting, but another rising edge will restart the count from the beginning.

- Modes 2 and 3: GATE low forces OUT high immediately (without waiting for a clock pulse) and resets the counter (on the next clock falling edge). When GATE goes high again, counting restarts from the beginning.

Mode 0 (000): Interrupt on terminal count

Mode 0 is used for the generation of accurate time delay under software control. In this mode, the counter will start counting from the initial COUNT value loaded into it, down to 0. Counting rate is equal to the input clock frequency.

The OUT pin is set low after the Control Word is written, and counting starts one clock cycle after the COUNT is programmed. OUT remains low until the counter reaches 0, at which point OUT will be set high until the counter is reloaded or the Control Word is written. The counter wraps around to 0xFFFF internally and continues counting, but the OUT pin never changes again. The Gate signal should remain active high for normal counting. If Gate goes low, counting is suspended, and resumes when it goes high again.

The first byte of the new count when loaded in the count register, stops the previous count.

Mode 1 (001): programmable one shot

In this mode 8253 can be used as a Monostable multivibrator. GATE input is used as trigger input.

OUT will be initially high. OUT will go low on the Clock pulse following a trigger to begin the one-shot pulse, and will remain low until the Counter reaches zero. OUT will then go high and remain high until the CLK pulse after the next trigger.

After writing the Control Word and initial count, the Counter is armed. A trigger results in loading the Counter and setting OUT low on the next CLK pulse, thus starting the one-shot pulse. An initial count of N will result in a one-shot pulse N CLK cycles in duration.

The one-shot is retriggerable, hence OUT will remain low for N CLK pulses after any trigger. The one-shot pulse can be repeated without rewriting the same count into the counter. GATE has no effect on OUT. If a new count is written to the Counter during a oneshot pulse, the current one-shot is not affected unless the counter is retriggered. In that case, the Counter is loaded with the new count and the oneshot pulse continues until the new count expires.

Mode 2 (X10): rate generator

In this mode, the device acts as a divide-by-n counter, which is commonly used to generate a real-time clock interrupt.

Like other modes, the counting process will start the next clock cycle after COUNT is sent. OUT will then remain high until the counter reaches 1, and will go low for one clock pulse. The following cycle, the count is reloaded, OUT goes high again, and the whole process repeats itself.

The time between the high pulses depends on the preset count in the counter's register, and is calculated using the following formula:

Value to be loaded into counter =

Note that the values in the COUNT register range from to 1; the register never reaches zero.

Mode 3 (X11): square wave generator

This mode is similar to mode 2. However, the duration of the high and low clock pulses of the output will be different from mode 2.

Suppose is the number loaded into the counter (the COUNT message), the output will be high for counts, and low for counts. Thus, the period will be counts, and if is odd, the extra half-cycle is spent with OUT high.

Mode 4 (100): Software Triggered Strobe

After Control Word and COUNT is loaded, the output will remain high until the counter reaches zero. The counter will then generate a low pulse for 1 clock cycle (a strobe) – after that the output will become high again.

GATE low suspends the count, which resumes when GATE goes high again.

Mode 5 (101): Hardware Triggered Strobe

This mode is similar to mode 4. However, the counting process is triggered by the GATE input.

After receiving the Control Word and COUNT, the output will be set high. Once the device detects a rising edge on the GATE input, it will start counting. When the counter reaches 0, the output will go low for one clock cycle – after that it will become high again, to repeat the cycle on the next rising edge of GATE.

IBM PC programming tips and hints

The 8253 was used in IBM PC compatibles since their introduction in 1981.[7] In modern times, this PIT is not included as a separate chip in an x86 PC. Rather, its functionality is included as part of the motherboard chipset's southbridge. In a modern chipset, this change may show up in the form of noticeably faster access to the PIT's registers in the x86 I/O address space.

All PC compatibles operate the PIT at a clock rate of 105/88 = 1.19318 MHz, 1⁄3 the NTSC colorburst frequency. This frequency, divided by 216 (the largest divisor the 8253 is capable of) produces the ≈18.2 Hz timer interrupt used in MS-DOS and related operating systems.

In the original IBM PCs, Counter 0 is used to generate a timekeeping interrupt. Counter 1 (A1=0, A0=1) is used to trigger the refresh of DRAM memory. The last counter (A1=1, A0=0) is used to generate tones via the PC speaker.

Newer motherboards include additional counters through the Advanced Configuration and Power Interface (ACPI), a counter on the Local Advanced Programmable Interrupt Controller (Local APIC), and a High Precision Event Timer. The CPU itself also provides the Time Stamp Counter (TSC) facility.

On PCs the address for timer0 (chip) is at port 40h..43h and the second timer1 (chip) is at 50h..53h.

On x86 PCs, many video card BIOS and system BIOS will reprogram the second counter for their own use. Reprogramming typically happens during video mode changes, when the video BIOS may be executed, and during system management mode and power saving state changes, when the system BIOS may be executed. This prevents any serious alternative uses of the timer's second counter on many x86 systems.

The timer that is used by the system on x86 PCs is Channel 0, and its clock ticks at a theoretical value of 1193181.8181... Hz, i.e. one third of the NTSC color subcarrier frequency, which comes from dividing the system clock (14.31818 MHz) by 12. This is a holdover of the very first CGA PCs – they derived all necessary frequencies from a single quartz crystal, and to make TV output possible, this oscillator had to run at a multiple of the NTSC color subcarrier frequency.

As stated above, Channel 0 is implemented as a counter. Typically, the initial value of the counter is set by sending bytes to the Control, then Data I/O Port registers (the value 36h sent to port 43h, then the low byte to port 40h, and port 40h again for the high byte). The counter counts down to zero, then sends a hardware interrupt (IRQ 0, INT 8) to the CPU. The counter then resets to its initial value and begins to count down again. The fastest possible interrupt frequency is a little over a half of a megahertz. The slowest possible frequency, which is also the one normally used by computers running MS-DOS or compatible operating systems, is about 18.2 Hz. Under these real mode operating systems, the BIOS accumulates the number of INT 8 calls that it receives in real mode address 0040:006c, which can be read by a program.

As a timer counts down, its value can also be read directly by reading its I/O port twice, first for the low byte, and then for the high byte. However, in free-running counter applications such as in the x86 PC, it is necessary to first write a latch command for the desired channel to the control register, so that both bytes read will belong to one and the same value.

According to a 2002 Microsoft document, "because reads from and writes to this hardware [8254] require communication through an IO port, programming it takes several cycles, which is prohibitively expensive for the OS. Because of this, the aperiodic functionality is not used in practice."[8]

References

- "Intel 82C54 CHMOS Programmabe Interval Timer" (PDF) (datasheet). Archived from the original (PDF) on 7 May 2016.

- D.A. Godse; A.P. Godse (2007). Advanced Microprocessors. Technical Publications. p. 74. ISBN 978-81-89411-33-6.

- http://pdf.datasheetcatalog.com/datasheet/Intel/mXvqwzr.pdf

- Intel Corporation, "Focus Components: Military Intelligence: Timers, EPROMs, Leadless Chip Carriers", Solutions, March/April 1983, Page 12.

- "8254/82C54: Introduction to Programmable Interval Timer". Intel Corporation. Archived from the original on 22 November 2016. Retrieved 21 August 2011.

- "MSM 82c53 Datasheet" (PDF).

- "Guidelines For Providing Multimedia Timer Support". 20 September 2002. Retrieved 13 October 2010.

- Guidelines For Providing Multimedia Timer Support

Further reading

- Gilluwe, Frank Van (1997). The Undocumented PC: A Programmer's Guide to I/O, CPUs, and Fixed Memory Areas (second, illustrated ed.). Addison-Wesley. ISBN 978-0-201-47950-8.