Cyclops64

Cyclops64 (formerly known as Blue Gene/C) is a cellular architecture in development by IBM. The Cyclops64 project aims to create the first "supercomputer on a chip".

History

Cyclops64 is part of the Blue Gene effort, to produce the next several generations of supercomputers. The projects were started in response to the announced construction of the Earth Simulator.

Cyclops64 is a cooperative project between the United States Department of Energy (which is partially funding the project), the U.S. Department of Defense, industry (IBM in particular), and academia.

The architecture was conceived by Seymour Cray Award winner Monty Denneau, who is currently leading the project.

Architecture overview

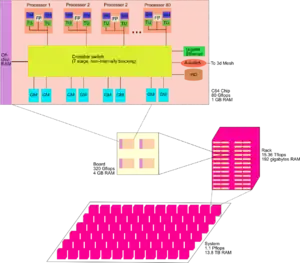

Each 64-bit Cyclops64 chip (processor) will run at 500 megahertz and contain 80 processors. Each processor will have two thread units and a floating point unit. A thread unit is an in-order 64-bit RISC core with 32 kB scratch pad memory, using a 60-instruction subset of the Power ISA instruction set. Five processors share a 32 kB instruction cache.

The processors will be connected with a 96 port, 7 stage non-internally blocking crossbar switch. They will communicate with each other via global interleaved memory (memory that can be written to and read by all threads) in the SRAM.

The theoretical peak performance of a Cyclops64 chip is 80 gigaflops (this assumes a continuous stream of multiply–accumulate instructions, each of which are counted as two floating-point operations). A full system (consisting of 2 thread units per processor, 80 processors per chip, 1 chip per board, 48 boards per midplane, 3 midplanes per rack, and 96 (12 x 8) racks per system) would contain 13,824 C64 chips, consisting of 1,105,920 processors capable of running 2,211,840 concurrent threads.

Software

Cyclops64 exposes much of the underlying hardware to the programmer, allowing the programmer to write very high performance, finely tuned software. One negative consequence is that efficiently programming Cyclops64 is difficult.

The system is expected to support TiNy-Threads (a threading library developed at the University of Delaware) and POSIX Threads.

Design and fabrication

Verification testing and system software development is being done at the University of Delaware.