Digital down converter

In digital signal processing, a digital down-converter (DDC) converts a digitized, band-limited signal to a lower frequency signal at a lower sampling rate in order to simplify the subsequent radio stages. The process can preserve all the information in the frequency band of interest of the original signal. The input and output signals can be real or complex samples. Often the DDC converts from the raw radio frequency or intermediate frequency down to a complex baseband signal.

Architecture

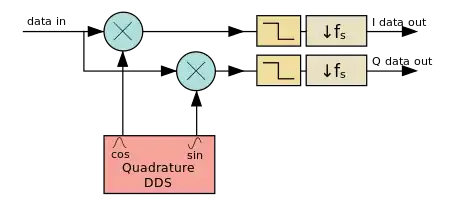

A DDC consists of three subcomponents: a direct digital synthesizer (DDS), a low-pass filter (LPF), and a downsampler (which may be integrated into the low-pass filter).

The DDS generates a complex sinusoid at the intermediate frequency (IF). Multiplication of the intermediate frequency with the input signal creates images centered at the sum and difference frequency (which follows from the frequency shifting properties of the Fourier transform). The lowpass filters pass the difference (i.e. baseband) frequency while rejecting the sum frequency image, resulting in a complex baseband representation of the original signal. Assuming judicious choice of IF and LPF bandwidth, the complex baseband signal is mathematically equivalent to the original signal. In its new form, it can readily be downsampled and is more convenient to many DSP algorithms.

Any suitable low-pass filter can be used including FIR, IIR and CIC filters. The most common choice is a FIR filter for low amounts of decimation (less than ten) or a CIC filter followed by a FIR filter for larger downsampling ratios.

Variations on the DDC

Several variations on the DDC are useful, including many that input a feedback signal into the DDS. These include:

- Decision directed carrier recovery phase locked loops in which the I and Q are compared to the nearest ideal constellation point of a PSK signal, and the resulting error signal is filtered and fed back into the DDS

- A Costas loop in which the I and Q are multiplied and low pass filtered as part of a BPSK/QPSK carrier recovery loop

Implementation

DDCs are most commonly implemented in logic in field-programmable gate arrays or application-specific integrated circuits. While software implementations are also possible, operations in the DDS, multipliers and input stages of the lowpass filters all run at the sampling rate of the input data. This data is commonly taken directly from analog-to-digital converters (ADCs) sampling at tens or hundreds of MHz.

CORDICs are an alternative to the use of multipliers in the implementation of digital down converters.[1]

Notes

- M. Loehning, T. Hentschel and G. Fettweis, "Digital Down Conversion in Software Radio Terminals", 10th European Signal Processing Conference, EUSIPCO 2000, pp 1517-1520, (2000).