High Threshold Logic

High Threshold Logic (HTL) is a variant of Diode–transistor logic which is used in such environments where noise is very high.

Operation

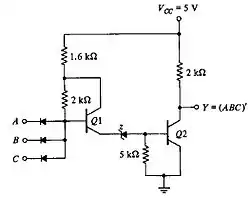

The threshold values at the input to a logic gate determine whether a particular input is interpreted as a logic 0 or a logic 1.(e.g. anything less than 1 V is a logic 0 and anything above 3 V is a logic 1. In this example, the threshold values are 1V and 3V). HTL incorporates Zener diodes to create a large offset between logic 1 and logic 0 voltage levels. These devices usually ran off a 15 V power supply and were found in industrial control, where the high differential was intended to minimize the effect of noise.

Advantages

- Increased Noise Margin

- Spike Control

- High Noise Threshold Value

Disadvantage

- Slow speed due to increased supply voltage resulting in use of high value resistors.

- High power drawn

Usage

It is used extensively in industrial environments. e.g.

- Logic Controllers with heavy noise

- Heavy Process Machinery

Circuital peculiarity

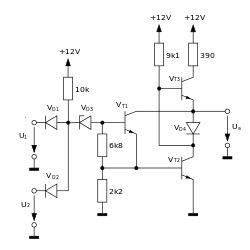

The buffer in this device is exactly the same of what was used in RGB video output stages in TV circuits in this way the upper NPN rises quickly a cathode capacitance with a relatively high load resistor on lower NPN, while lower NPN turn-on controls carefully K voltage

This shows the same improvement in charge-discharge parasitic capacitances in such high voltage logic circuit

See also

- Diode logic (DL)

- Emitter-coupled logic (ECL)

- Integrated injection logic (I2L)

- Resistor–transistor logic (RTL)

- Transistor–transistor logic (TTL)