NMOS logic

N-type metal-oxide-semiconductor logic uses n-type (-) MOSFETs (metal-oxide-semiconductor field-effect transistors) to implement logic gates and other digital circuits. These nMOS transistors operate by creating an inversion layer in a p-type transistor body. This inversion layer, called the n-channel, can conduct electrons between n-type "source" and "drain" terminals. The n-channel is created by applying voltage to the third terminal, called the gate. Like other MOSFETs, nMOS transistors have four modes of operation: cut-off (or subthreshold), triode, saturation (sometimes called active), and velocity saturation.

Overview

MOS stands for metal-oxide-semiconductor, reflecting the way MOS-transistors were originally constructed, predominantly before the 1970s, with gates of metal, typically aluminium. Since around 1970, however, most MOS circuits have used self-aligned gates made of polycrystalline silicon, a technology first developed by Federico Faggin at Fairchild Semiconductor. These silicon gates are still used in most types of MOSFET based integrated circuits, although metal gates (Al or Cu) started to reappear in the early 2000s for certain types of high speed circuits, such as high performance microprocessors.

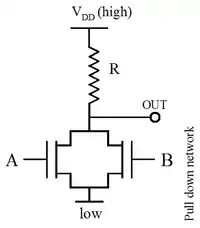

The MOSFETs are n-type enhancement mode transistors, arranged in a so-called "pull-down network" (PDN) between the logic gate output and negative supply voltage (typically the ground). A pull up (i.e. a "load" that can be thought of as a resistor, see below) is placed between the positive supply voltage and each logic gate output. Any logic gate, including the logical inverter, can then be implemented by designing a network of parallel and/or series circuits, such that if the desired output for a certain combination of boolean input values is zero (or false), the PDN will be active, meaning that at least one transistor is allowing a current path between the negative supply and the output. This causes a voltage drop over the load, and thus a low voltage at the output, representing the zero.

As an example, here is a NOR gate implemented in schematic NMOS. If either input A or input B is high (logic 1, = True), the respective MOS transistor acts as a very low resistance between the output and the negative supply, forcing the output to be low (logic 0, = False). When both A and B are high, both transistors are conductive, creating an even lower resistance path to ground. The only case where the output is high is when both transistors are off, which occurs only when both A and B are low, thus satisfying the truth table of a NOR gate:

| A | B | A NOR B |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

A MOSFET can be made to operate as a resistor, so the whole circuit can be made with n-channel MOSFETs only. NMOS circuits are slow to transition from low to high. When transitioning from high to low, the transistors provide low resistance, and the capacitive charge at the output drains away very quickly (similar to discharging a capacitor through a very low resistor). But the resistance between the output and the positive supply rail is much greater, so the low to high transition takes longer (similar to charging a capacitor through a high value resistor). Using a resistor of lower value will speed up the process but also increases static power dissipation. However, a better (and the most common) way to make the gates faster is to use depletion-mode transistors instead of enhancement-mode transistors as loads. This is called depletion-load NMOS logic.

For many years, NMOS circuits were much faster than comparable PMOS and CMOS circuits, which had to use much slower p-channel transistors. It was also easier to manufacture NMOS than CMOS, as the latter has to implement p-channel transistors in special n-wells on the p-substrate. The major drawback with NMOS (and most other logic families) is that a DC current must flow through a logic gate even when the output is in a steady state (low in the case of NMOS). This means static power dissipation, i.e. power drain even when the circuit is not switching. A similar situation arises in modern high speed, high density CMOS circuits (microprocessors, etc.) which also has significant static current draw, although this is due to leakage, not bias. However, older and/or slower static CMOS circuits used for ASICs, SRAM, etc., typically have very low static power consumption.

Additionally, just like in DTL, TTL, ECL, etc., the asymmetric input logic levels make NMOS and PMOS circuits more susceptible to noise than CMOS. These disadvantages are why the CMOS logic now has supplanted most of these types in most high-speed digital circuits such as microprocessors (despite the fact that CMOS was originally very slow compared to logic gates built with bipolar transistors).

History

The MOSFET was invented by Egyptian engineer Mohamed M. Atalla and Korean engineer Dawon Kahng at Bell Labs in 1959, and demonstrated in 1960.[1] They fabricated both PMOS and NMOS devices with a 20 µm process. However, the NMOS devices were impractical, and only the PMOS type were practical devices.[2]

In 1965, Chih-Tang Sah, Otto Leistiko and A.S. Grove at Fairchild Semiconductor fabricated several NMOS devices with channel lengths between 8 µm and 65 µm.[3] Dale L. Critchlow and Robert H. Dennard at IBM also fabricated NMOS devices in the 1960s. The first IBM NMOS product was a memory chip with 1 kb data and 50–100 ns access time, which entered large-scale manufacturing in the early 1970s. This led to MOS semiconductor memory replacing earlier bipolar and ferrite-core memory technologies in the 1970s.[4]

The earliest microprocessors in the early 1970s were PMOS processors, which initially dominated the early microprocessor industry.[5] In 1973, NEC's μCOM-4 was an early NMOS microprocessor, fabricated by the NEC LSI team, consisting of five researchers led by Sohichi Suzuki.[6][7] By the late 1970s, NMOS microprocessors had overtaken PMOS processors.[5] CMOS microprocessors were introduced in 1975.[5][8][9] However, CMOS processors did not become dominant until the 1980s.[5]

CMOS was initially slower than NMOS logic, thus NMOS was more widely used for computers in the 1970s.[10] The Intel 5101 (1 kb SRAM) CMOS memory chip (1974) had an access time of 800 ns,[11][12] whereas the fastest NMOS chip at the time, the Intel 2147 (4 kb SRAM) HMOS memory chip (1976), had an access time of 55/70 ns.[10][12] In 1978, a Hitachi research team led by Toshiaki Masuhara introduced the twin-well Hi-CMOS process, with its HM6147 (4 kb SRAM) memory chip, manufactured with a 3 µm process.[10][13] The Hitachi HM6147 chip was able to match the performance (55/70 ns access) of the Intel 2147 HMOS chip, while the HM6147 also consumed significantly less power (15 mA) than the 2147 (110 mA). With comparable performance and much less power consumption, the twin-well CMOS process eventually overtook NMOS as the most common semiconductor manufacturing process for computers in the 1980s.[10]

In the 1980s, CMOS microprocessors overtook NMOS microprocessors.[5]

See also

- PMOS logic

- Depletion-load NMOS logic (including the processes called HMOS (high density, short channel MOS), HMOS-II, HMOS-III, etc. A family of high performance manufacturing processes for depletion-load NMOS logic circuits that was developed by Intel in the late 1970s and used for many years. Several CMOS manufacturing processes such as CHMOS, CHMOS-II, CHMOS-III, etc., descended directly from these NMOS-processes.

References

- "1960 - Metal Oxide Semiconductor (MOS) Transistor Demonstrated". The Silicon Engine. Computer History Museum.

- Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. pp. 321–3. ISBN 9783540342588.

- Sah, Chih-Tang; Leistiko, Otto; Grove, A. S. (May 1965). "Electron and hole mobilities in inversion layers on thermally oxidized silicon surfaces". IEEE Transactions on Electron Devices. 12 (5): 248–254. Bibcode:1965ITED...12..248L. doi:10.1109/T-ED.1965.15489.

- Critchlow, D. L. (2007). "Recollections on MOSFET Scaling". IEEE Solid-State Circuits Society Newsletter. 12 (1): 19–22. doi:10.1109/N-SSC.2007.4785536.

- Kuhn, Kelin (2018). "CMOS and Beyond CMOS: Scaling Challenges". High Mobility Materials for CMOS Applications. Woodhead Publishing. p. 1. ISBN 9780081020623.

- "1970s: Development and evolution of microprocessors" (PDF). Semiconductor History Museum of Japan. Retrieved 27 June 2019.

- "NEC 751 (uCOM-4)". The Antique Chip Collector's Page. Archived from the original on 2011-05-25. Retrieved 2010-06-11.

- Cushman, Robert H. (20 September 1975). "2-1/2-generation μP's-$10 parts that perform like low-end mini's" (PDF). EDN. Archived from the original (PDF) on 24 April 2016. Retrieved 15 September 2019.

- "CDP 1800 μP Commercially available" (PDF). Microcomputer Digest. 2 (4): 1–3. October 1975.

- "1978: Double-well fast CMOS SRAM (Hitachi)" (PDF). Semiconductor History Museum of Japan. Archived from the original (PDF) on 5 July 2019. Retrieved 5 July 2019.

- "Silicon Gate MOS 2102A". Intel. Retrieved 27 June 2019.

- "A chronological list of Intel products. The products are sorted by date" (PDF). Intel museum. Intel Corporation. July 2005. Archived from the original (PDF) on August 9, 2007. Retrieved July 31, 2007.

- Masuhara, Toshiaki; Minato, O.; Sasaki, T.; Sakai, Y.; Kubo, M.; Yasui, T. (1978). "A high-speed, low-power Hi-CMOS 4K static RAM". 1978 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. XXI: 110–111. doi:10.1109/ISSCC.1978.1155749.

External links

Media related to MOS at Wikimedia Commons

Media related to MOS at Wikimedia Commons