Wafer dicing

In the context of manufacturing integrated circuits, wafer dicing is the process by which die are separated from a wafer of semiconductor following the processing of the wafer. The dicing process can involve scribing and breaking, mechanical sawing (normally with a machine called a dicing saw)[1] or laser cutting. All methods are typically automated to ensure precision and accuracy.[2] Following the dicing process the individual silicon chips are encapsulated into chip carriers which are then suitable for use in building electronic devices such as computers, etc.

During dicing, wafers are typically mounted on dicing tape which has a sticky backing that holds the wafer on a thin sheet metal frame. Dicing tape has different properties depending on the dicing application. UV curable tapes are used for smaller sizes and non-UV dicing tape for larger die sizes. Once a wafer has been diced, the pieces left on the dicing tape are referred to as die, dice or dies. Each will be packaged in a suitable package or placed directly on a printed circuit board substrate as a "bare die". The areas that have been cut away, called die streets, are typically about 75 micrometres (0.003 inch) wide. Once a wafer has been diced, the die will stay on the dicing tape until they are extracted by die-handling equipment, such as a die bonder or die sorter, further in the electronics assembly process.

The size of the die left on the tape may range from 35 mm (very large) to 0.1 mm square (very small). The die created may be any shape generated by straight lines, but they are typically rectangular or square-shaped. In some cases they can be other shapes as well depending on the singulation method used. A full-cut laser dicer has the ability to cut and separate in a variety of shapes.

Materials diced include glass, alumina, silicon, gallium arsenide (GaAs), silicon on sapphire (SoS), Ceramics, and delicate compound semiconductors.

Stealth dicing

Dicing of silicon wafers may also be performed by a laser-based technique, the so-called stealth dicing process. It works as a two-stage process in which defect regions are firstly introduced into the wafer by scanning the beam along intended cutting lines and secondly an underlying carrier membrane is expanded to induce fracture.[4]

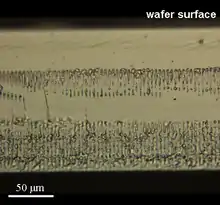

The first step operates with a pulsed Nd:YAG laser, the wavelength of which (1064 nm) is well adapted to the electronic band gap of silicon (1.11 eV or 1117 nm), so that maximum absorption may well be adjusted by optical focusing.[5] Defect regions of about 10 µm width are inscribed by multiple scans of the laser along the intended dicing lanes, where the beam is focused at different depths of the wafer.[6] The figure displays an optical micrograph of a cleavage plane of a separated chip of 150 µm thickness that was subjected to four laser scans, compare.[3] The topmost defects are the best resolved and it is realized that a single laser pulse causes a defected crystal region that resembles the shape of candle flame. This shape is caused by the rapid melting and solidification of the irradiated region in the laser beam focus, where the temperature of only some µm3 small volumes suddenly rises to some 1000 K within nanoseconds and falls to ambient temperature again.[5][6] The laser is typically pulsed by a frequency of about 100 kHz, while the wafer is moved with a velocity of about 1 m/s. A defected region of about 10 µm width is finally inscribed in the wafer, along which preferential fracture occurs under mechanical loading. The fracture is performed in the second step and operates by radially expanding the carrier membrane to which the wafer is attached. The cleavage initiates at the bottom and advances to the surface, from which it is understood that a high distortion density must be introduced at the bottom.

It is the advantage of the stealth dicing process that it does not require a cooling liquid. Dry dicing methods inevitably have to be applied for the preparation of certain microelectromechanical systems (MEMS), in particular, when these are intended for bioelectronic applications.[3] In addition, stealth dicing hardly generates debris and allows for improved exploitation of the wafer surface due to smaller kerf loss compared to wafer saw. Wafer grinding may be performed after this step, to reduce die thickness.[7]

Dice before grind

The DBG or "dice before grind" process is a way to separate dies without dicing. The separation occurs during the wafer thinning step. The wafers are initially diced using a half-cut dicer to a depth below the final target thickness. Next, the wafer is thinned to the target thickness while mounted on a special adhesive film[8] and then mounted on to a pick-up tape to hold the dies in place until they are ready for the packaging step. The benefit to the DBG process is higher die strength.[9] Alternatively, plasma dicing may be used, which replaces the dicer's saw with DRIE plasma etching.[10][11][12][13][14][15][16][17]

The DBG process requires a back grinding tape that has the following attributes, 1) strong adhesive force (Prevents infiltration of grinding fluid and die dust during grinding), 2) absorption and/or relief of compression stress and shear stress during grinding, 3) suppresses cracking due to contact between dies, 4) adhesive strength that can be greatly reduced through UV irradiation.[18]

See also

References

- "Key Wafer Sawing Factors". Optocap. Retrieved 14 April 2013.

- http://www.syagrussystems.com/service-overview

- M. Birkholz; K.-E. Ehwald; M. Kaynak; T. Semperowitsch; B. Holz; S. Nordhoff (2010). "Separation of extremely miniaturized medical sensors by IR laser dicing". J. Opto. Adv. Mat. 12: 479–483.

- Kumagai, M.; Uchiyama, N.; Ohmura, E.; Sugiura, R.; Atsumi, K.; Fukumitsu, K. (August 2007). "Advanced Dicing Technology for Semiconductor Wafer—Stealth Dicing". IEEE Transactions on Semiconductor Manufacturing. 20 (3): 259–265. doi:10.1109/TSM.2007.901849. S2CID 6034954.

- E. Ohmura, F. Fukuyo, K. Fukumitsu and H. Morita (2006). "Internal modified layer formation mechanism into silicon with nanosecond laser". J. Achiev. Mat. Manuf. Eng. 17: 381–384.CS1 maint: multiple names: authors list (link)

- M. Kumagai, N. Uchiyama, E. Ohmura, R. Sugiura, K. Atsumi and K. Fukumitsu (2007). "Advanced Dicing Technology for Semiconductor Wafer – Stealth Dicing". IEEE Transactions on Semiconductor Manufacturing. 20 (3): 259–265. doi:10.1109/TSM.2007.901849. S2CID 6034954.CS1 maint: multiple names: authors list (link)

- https://www.disco.co.jp/eg/solution/library/sdbg.html

- https://www.disco.co.jp/eg/solution/library/dbg.html

- "Semiconductor Dicing Tapes". Semiconductor Dicing Tapes. Retrieved 14 April 2013.

- "Plasma Dicing | Orbotech". www.orbotech.com.

- "APX300 : Plasma Dicer - Industrial Devices & Solutions - Panasonic". industrial.panasonic.com.

- "Plasma Dicing of Silicon & III-V (GaAs, InP & GaN)". SAMCO Inc.

- https://www.researchgate.net/figure/Example-of-plasma-dicing-process_fig17_283434064/amp

- "Plasma-Therm: Plasma Dicing". www.plasmatherm.com.

- https://www.samcointl.com/tech_notes/pdf/Technical_Report_87.pdf

- http://www.plasma-therm.com/pdfs/papers/CSR-Plasma-Dicing-Methods-Thin-Wafers.pdf

- "Plasma Dicing (Dice Before Grind) | Orbotech". www.orbotech.com.

- Products for DBG Process (LINTEC) http://www.lintec-usa.com/di_dbg.cfm