mP6

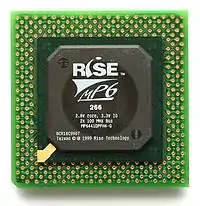

The Rise mP6 was a superpipelined and superscalar[3] microprocessor designed by Rise Technology to compete with the Intel Pentium line.

| |

| General information | |

|---|---|

| Launched | 1998 |

| Discontinued | 1999 |

| Marketed by | Rise Technology |

| Designed by | Rise Technology |

| Common manufacturer(s) | |

| CPUID code | 00000504 (Kirin) 00000521 (Lynx)[2] |

| Product code | 6441 |

| Performance | |

| Max. CPU clock rate | 166 MHz to 250 MHz |

| FSB speeds | 83 Mhz to 100 Mhz |

| Cache | |

| L1 cache | 16 KiB |

| L2 cache | Motherboard dependent |

| L3 cache | none |

| Architecture and classification | |

| Min. feature size | 0.25 µm to 0.18 µm |

| Microarchitecture | 8-stage (integer)/4-stage (Floating point), triple pipelined design |

| Instruction set | x86 (IA-32) |

| Physical specifications | |

| Cores |

|

| Package(s) | |

| Socket(s) | |

| Products, models, variants | |

| Core name(s) |

|

| History | |

| Successor | Rise mP6-II |

History

Rise Technology had spent 5 years developing a x86 compatible microprocessor,[4] and finally introduced it in November 1998 as a low-cost, low-power alternative for the Super Socket 7 platform, that allowed for higher Front-side bus speeds than the previous Socket 7 and that made it possible for other CPU manufacturers to keep competing against Intel, that had moved to the Slot 1 platform.

Design

The mP6 made use of the MMX instruction set and had three MMX pipelines which allowed the CPU to execute up to three MMX instructions in a single cycle. Its three integer units made it possible to execute three integer instructions in a single cycle as well and the fully pipelined floating point unit could execute up to two floating-point instructions per cycle. To further improve the performance the core utilized branch prediction and a number of techniques to resolve data dependency conflicts.[3] According to Rise, the mP6 should perform almost as fast as Intel Pentium II at the same frequencies.[5]

Performance

Despite its innovative features, the real-life performance of the mP6 proved disappointing. This was mainly due to the small L1 Cache.[5] Another reason was that the Rise mP6's PR 266 rating was based upon the old Intel Pentium MMX,[5] while its main competitors were the Intel Celeron 266, the IDT WinChip 2-266 and the AMD K6-2 266, that all delivered more performance in most benchmarks and applications.[5] The Celeron and the K6-2 actually worked at 266 MHz, and the WinChip 2's PR rating was based upon the performance of its AMD opponent.[5]

Legacy

Silicon Integrated Systems (SiS) licensed the mP6 technology, and used it in the SiS 550, a system-on-a-chip (SoC) that integrated the mP6 CPU, the north and south bridges, and sound and video on a single chip. The SiS 550 saw use in some compact PCs and in consumer devices, such as DVD players. The SiS 551 chip was also marketed by DM&P as Vortex86 (M6127D).

Later DM&P took over mP6 design from SiS and continues development under Vortex86 SoC product line.

DM&P further signed an agreement with Xcore to allow them to rebrand the chip as Xcore86.[6]

mP6 data

| Model number | Frequency | L1 Cache | FSB | Mult. | Voltage | TDP | Socket | Release date | Part number(s) | sSpec number | Introduction price |

|---|---|---|---|---|---|---|---|---|---|---|---|

| PR 166 | 166 MHz | 8 (data) + 8 (instructions) KB | 83 Mhz | 2x | 2.75–2.85 V | 7.28 W | Super Socket 7 BGA 387 PPGA 296 | 13 October 1998 | MP6441RPFE4-Q | $50 | |

| PR 233 | 190 MHz | 8 (data) + 8 (instructions) KB | 95 Mhz | 2x | 2.75–2.85 V | 8.11 W | Super Socket 7 BGA 387 PPGA 296 | 13 October 1998 | |||

| PR 266 | 200 MHz | 8 (data) + 8 (instructions) KB | 100 Mhz | 2x | 2.75–2.85 V | 8.54 W | Super Socket 7 BGA 387 PPGA 296 | 13 October 1998 | MP6441DPFH4-Q MP6441RPFH4-Q | $70 | |

| PR 333 | 240 MHz | 8 (data) + 8 (instructions) KB | 95 Mhz | 2.5x | 2 V | 10.18 W | Super Socket 7 BGA 387 PPGA 296 | 26 May 1999 Samples only | MP65RPAPG5-ES | ||

| PR 366[7] | 250 MHz | 8 (data) + 8 (instructions) KB | 100 Mhz | 2.5x | 2 V | 10.72 W | Super Socket 7 BGA 387 PPGA 296 | 26 May 1999 Samples only | MP65RPAPH5-DS |

References

- "32 BITS: SUPERSCALAR: 4.26. Rise iDragon mP6". Archived from the original on 21 April 2012. Retrieved 3 November 2011.

- "x86, x64 Instruction Latency, Memory Latency and CPUID dumps". 22 October 2011. Retrieved 3 November 2011.

- Shvets, Gennadiy (8 October 2011). "Rise Technology MP6 family". CPU World. Retrieved 1 November 2011.

- "Rise mP6". CPU-collection.de. Retrieved 1 November 2011.

- Gravrichenkov, Ilya (15 May 1999). "Rise mP6 266 Review". X-bit Laboratories. Archived from the original on 7 May 2009. Retrieved 1 November 2011.

- Xcore Corporation Ltd. has entered into an agreement with DMP Electronics Inc. Archived 2009-04-04 at the Wayback Machine

- Shvets, Gennadiy (8 October 2011). "Rise Technology MP6 PR 366". CPU World. Retrieved 1 November 2011.