Intel Core (microarchitecture)

The Intel Core microarchitecture (formerly named Next-Generation Micro-Architecture) is a multi-core processor microarchitecture unveiled by Intel in Q1 2006. It is based on the Yonah processor design and can be considered an iteration of the P6 microarchitecture introduced in 1995 with Pentium Pro. High power consumption and heat intensity, the resulting inability to effectively increase clock rate, and other shortcomings such as an inefficient pipeline were the primary reasons why Intel abandoned the NetBurst microarchitecture and switched to a different architectural design, delivering high efficiency through a small pipeline rather than high clock rates. The Core microarchitecture initially did not reach the clock rates of the NetBurst microarchitecture, even after moving to 45 nm lithography. However after many generations of successor microarchitectures which used Core as their basis (such as Nehalem, Sandy Bridge and more), Intel managed to eventually surpass the clock rates of Netburst with the Devil's Canyon (Improved version of Haswell) microarchitecture reaching a base frequency of 4 GHz and a maximum tested frequency of 4.4 GHz using 22 nm lithography.

| General information | |

|---|---|

| Launched | July 27, 2006 |

| Performance | |

| Max. CPU clock rate | 1.06 GHz to 3.33 GHz |

| FSB speeds | 533 MT/s to 1600 MT/s |

| Cache | |

| L1 cache | 64 KB per core |

| L2 cache | 1 MB to 8 MB unified |

| L3 cache | 8 MB to 16 MB shared (Xeon) |

| Architecture and classification | |

| Min. feature size | 65 nm to 45 nm |

| Architecture | Intel Core x86 |

| Instructions | x86, x86-64 |

| Extensions | |

| Physical specifications | |

| Transistors |

|

| Cores |

|

| Socket(s) | |

| Products, models, variants | |

| Model(s) | |

| History | |

| Predecessor | NetBurst Enhanced Pentium M (P6) |

| Successor | Penryn (tick) Nehalem (tock) |

The first processors that used this architecture were code-named 'Merom', 'Conroe', and 'Woodcrest'; Merom is for mobile computing, Conroe is for desktop systems, and Woodcrest is for servers and workstations. While architecturally identical, the three processor lines differ in the socket used, bus speed, and power consumption. The initial mainstream Core-based processors were branded Pentium Dual-Core or Pentium and low end branded Celeron; server and workstation Core-based processors were branded Xeon, while Intel's first 64-bit desktop and mobile Core-based processors were branded Core 2.

Features

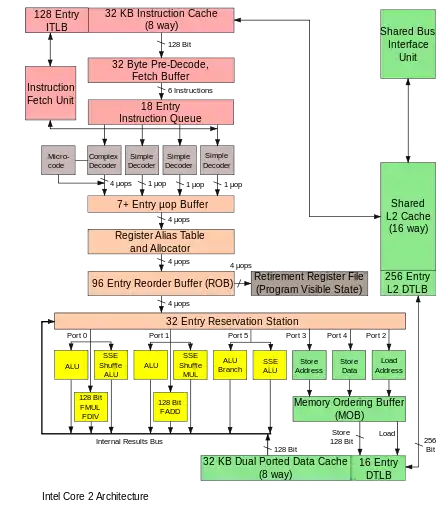

The Core microarchitecture returned to lower clock rates and improved the use of both available clock cycles and power when compared with the preceding NetBurst microarchitecture of the Pentium 4 and D-branded CPUs.[1] The Core microarchitecture provides more efficient decoding stages, execution units, caches, and buses, reducing the power consumption of Core 2-branded CPUs while increasing their processing capacity. Intel's CPUs have varied widely in power consumption according to clock rate, architecture, and semiconductor process, shown in the CPU power dissipation tables.

Like the last NetBurst CPUs, Core based processors feature multiple cores and hardware virtualization support (marketed as Intel VT-x), and Intel 64 and SSSE3. However, Core-based processors do not have the hyper-threading technology as in Pentium 4 processors. This is because the Core microarchitecture is based on the P6 microarchitecture used by Pentium Pro, II, III, and M.

The L1 cache size was enlarged in the Core microarchitecture, from 32 KB on Pentium II / III (16 KB L1 Data + 16 KB L1 Instruction) to 64 KB L1 cache/core (32 KB L1 Data + 32 KB L1 Instruction) on Pentium M and Core/Core 2. The consumer version also lacks an L3 cache as in the Gallatin core of the Pentium 4 Extreme Edition, though it is exclusively present in high-end versions of Core-based Xeons. Both an L3 cache and hyper-threading were reintroduced again to consumer line in the Nehalem microarchitecture.

Roadmap

Technology

While the Core microarchitecture is a major architectural revision it is based in part on the Pentium M processor family designed by Intel Israel.[2] The Penryn pipeline is 12–14 stages long[3] – less than half of Prescott's, a signature feature of wide order execution cores. Penryn's successor, Nehalem borrowed more heavily from the Pentium 4 and has 20-24 pipeline stages.[3] Core's execution unit is 4 issues wide, compared to the 3-issue cores of P6, Pentium M, and 2-issue cores of NetBurst microarchitectures. The new architecture is a dual core design with linked L1 cache and shared L2 cache engineered for maximum performance per watt and improved scalability.

One new technology included in the design is Macro-Ops Fusion, which combines two x86 instructions into a single micro-operation. For example, a common code sequence like a compare followed by a conditional jump would become a single micro-op. However, this technology does not work in 64-bit mode.

Other new technologies include 1 cycle throughput (2 cycles previously) of all 128-bit SSE instructions and a new power saving design. All components will run at minimum speed, raising speed dynamically as needed (similar to AMD's Cool'n'Quiet power-saving technology, and Intel's own SpeedStep technology from earlier mobile processors). This allows the chip to produce less heat, and minimize power use.

For most Woodcrest CPUs, the front-side bus (FSB) runs at 1333 MT/s; however, this is scaled down to 1066 MT/s for lower end 1.60 and 1.86 GHz variants.[4][5] The Merom mobile variant was initially targeted to run at an FSB of 667 MT/s while the second wave of Meroms, supporting 800 MT/s FSB, were released as part of the Santa Rosa platform with a different socket in May 2007. The desktop-oriented Conroe began with models having an FSB of 800 MT/s or 1066 MT/s with a 1333 MT/s line officially launched on July 22, 2007.

The power use of these new processors is very low: average energy use is to be in the 1–2 watt range in ultra low voltage variants, with thermal design powers (TDPs) of 65 watts for Conroe and most Woodcrests, 80 watts for the 3.0 GHz Woodcrest, and 40 watts for the low-voltage Woodcrest. In comparison, an AMD Opteron 875HE processor consumes 55 watts, while the energy efficient Socket AM2 line fits in the 35 watt thermal envelope (specified a different way so not directly comparable). Merom, the mobile variant, is listed at 35 watts TDP for standard versions and 5 watts TDP for ultra low voltage (ULV) versions.

Previously, Intel announced that it would now focus on power efficiency, rather than raw performance. However, at Intel Developer Forum (IDF) in spring 2006, Intel advertised both. Some of the promised numbers were:

- 20% more performance for Merom at the same power level; compared to Core Duo

- 40% more performance for Conroe at 40% less power; compared to Pentium D

- 80% more performance for Woodcrest at 35% less power; compared to the original dual-core Xeon

Processor cores

The processors of the Core microarchitecture can be categorized by number of cores, cache size, and socket; each combination of these has a unique code name and product code that is used across several brands. For instance, code name "Allendale" with product code 80557 has two cores, 2 MB L2 cache and uses the desktop socket 775, but has been marketed as Celeron, Pentium, Core 2, and Xeon, each with different sets of features enabled. Most of the mobile and desktop processors come in two variants that differ in the size of the L2 cache, but the specific amount of L2 cache in a product can also be reduced by disabling parts at production time. Wolfdale-DP and all quad-core processors except Dunnington QC are multi-chip modules combining two dies. For the 65 nm processors, the same product code can be shared by processors with different dies, but the specific information about which one is used can be derived from the stepping.

| fab | cores | Mobile | Desktop, UP Server | CL Server | DP Server | MP Server | |||

|---|---|---|---|---|---|---|---|---|---|

| Single-Core 65 nm | 65 nm | 1 | Merom-L 80537 | Conroe-L 80557 | |||||

| Single-Core 45 nm | 45 nm | 1 | Penryn-L 80585 | Wolfdale-CL 80588 | |||||

| Dual-Core 65 nm | 65 nm | 2 | Merom-2M 80537 | Merom 80537 | Allendale 80557 | Conroe 80557 | Conroe-CL 80556 | Woodcrest 80556 | Tigerton-DC 80564 |

| Dual-Core 45 nm | 45 nm | 2 | Penryn-3M 80577 | Penryn 80576 | Wolfdale-3M 80571 | Wolfdale 80570 | Wolfdale-CL 80588 | Wolfdale-DP 80573 | |

| Quad-Core 65 nm | 65 nm | 4 | Kentsfield 80562 | Clovertown 80563 | Tigerton 80565 | ||||

| Quad-Core 45 nm | 45 nm | 4 | Penryn-QC 80581 | Yorkfield-6M 80580 | Yorkfield 80569 | Yorkfield-CL 80584 | Harpertown 80574 | Dunnington QC 80583 | |

| Six-Core 45 nm | 45 nm | 6 | Dunnington 80582 | ||||||

Conroe/Merom (65 nm)

The original Core 2 processors are based on the same dies that can be identified as CPUID Family 6 Model 15. Depending on their configuration and packaging, their code names are Conroe (LGA 775, 4 MB L2 cache), Allendale (LGA 775, 2 MB L2 cache), Merom (Socket M, 4 MB L2 cache) and Kentsfield (multi-chip module, LGA 775, 2x4MB L2 cache). Merom and Allendale processors with limited features are in Pentium Dual Core and Celeron processors, while Conroe, Allendale and Kentsfield also are sold as Xeon processors.

Additional code names for processors based on this model are Woodcrest (LGA 771, 4 MB L2 cache), Clovertown (MCM, LGA 771, 2×4MB L2 cache) and Tigerton (MCM, Socket 604, 2×4MB L2 cache), all of which are marketed only under the Xeon brand.

| Processor | Brand name | Model (list) | Cores | L2 Cache | Socket | TDP |

|---|---|---|---|---|---|---|

| Merom-2M | Mobile Core 2 Duo | U7xxx | 2 | 2 MiB | BGA479 | 10 W |

| Merom | L7xxx | 4 MiB | 17 W | |||

| Merom Merom-2M |

T5xxx T7xxx | 2–4 MiB | Socket M Socket P BGA479 | 35 W | ||

| Merom | Mobile Core 2 Extreme | X7xxx | 2 | 4 MiB | Socket P | 44 W |

| Merom | Celeron M | 5x0 | 1 | 1 MiB | Socket M Socket P | 30 W |

| Merom-2M | 5x5 | Socket P | 31 W | |||

| Merom-2M | Celeron Dual-Core | T1xxx | 2 | 512–1024 KiB | Socket P | 35 W |

| Merom-2M | Pentium Dual-Core | T2xxx T3xxx | 2 | 1 MiB | Socket P | 35 W |

| Allendale | Xeon | 3xxx | 2 | 2 MB | LGA 775 | 65 W |

| Conroe | 3xxx | 2–4 MB | ||||

| Conroe and Allendale |

Core 2 Duo | E4xxx | 2 | 2 MB | LGA 775 | 65 W |

| E6xx0 | 2–4 MB | |||||

| Conroe-CL | E6xx5 | 2–4 MB | LGA 771 | |||

| Conroe-XE | Core 2 Extreme | X6xxx | 2 | 4 MB | LGA 775 | 75 W |

| Allendale | Pentium Dual-Core | E2xxx | 2 | 1 MB | LGA 775 | 65 W |

| Allendale | Celeron | E1xxx | 2 | 512 KB | LGA 775 | 65 W |

| Kentsfield | Xeon | 32xx | 4 | 2×4 MiB | LGA 775 | 95–105 W |

| Kentsfield | Core 2 Quad | Q6xxx | 4 | 2×4 MiB | LGA 775 | 95–105 W |

| Kentsfield XE | Core 2 Extreme | QX6xxx | 4 | 2×4 MiB | LGA 775 | 130 W |

| Woodcrest | Xeon | 51xx | 2 | 4 MB | LGA 771 | 65–80 W |

| Clovertown | L53xx | 4 | 2×4 MB | LGA 771 | 40–50 W | |

| E53xx | 80 W | |||||

| X53xx | 120–150 W | |||||

| Tigerton-DC | E72xx | 2 | 2×4 MB | Socket 604 | 80 W | |

| Tigerton | L73xx | 4 | 50 W | |||

| E73xx | 2×2–2×4 MB | 80 W | ||||

| X73xx | 2×4 MB | 130 W |

Conroe-L/Merom-L

The Conroe-L and Merom-L processors are based around the same core as Conroe and Merom, but only contain a single core and 1 MB of L2 cache, significantly reducing production cost and power consumption of the processor at the expense of performance compared to the dual-core version. It is used only in ultra-low voltage Core 2 Solo U2xxx and in Celeron processors and is identified as CPUID family 6 model 22.

| Processor | Brand name | Model (list) | Cores | L2 Cache | Socket | TDP |

|---|---|---|---|---|---|---|

| Merom-L | Mobile Core 2 Solo | U2xxx | 1 | 2 MiB | BGA479 | 5.5 W |

| Merom-L | Celeron M | 5x0 | 1 | 512 KiB | Socket M Socket P | 27 W |

| Merom-L | 5x3 | 512–1024 KiB | BGA479 | 5.5–10 W | ||

| Conroe-L | Celeron M | 4x0 | 1 | 512 KiB | LGA 775 | 35 W |

| Conroe-CL | 4x5 | LGA 771 | 65 W |

Penryn/Wolfdale (45 nm)

In Intel's Tick-Tock cycle, the 2007/2008 "Tick" was the shrink of the Core microarchitecture to 45 nanometers as CPUID model 23. In Core 2 processors, it is used with the code names Penryn (Socket P), Wolfdale (LGA 775) and Yorkfield (MCM, LGA 775), some of which are also sold as Celeron, Pentium and Xeon processors. In the Xeon brand, the Wolfdale-DP and Harpertown code names are used for LGA 771 based MCMs with two or four active Wolfdale cores.

Architecturally, 45nm Core 2 processors feature SSE4.1 and new divide/shuffle engine.[6]

The chips come in two sizes, with 6 MB and 3 MB L2 cache. The smaller version is commonly called Penryn-3M and Wolfdale-3M and Yorkfield-6M, respectively. The single-core version of Penryn, listed as Penryn-L here, is not a separate model like Merom-L but a version of the Penryn-3M model with only one active core.

| Processor | Brand name | Model (list) | Cores | L2 Cache | Socket | TDP |

|---|---|---|---|---|---|---|

| Penryn-L | Core 2 Solo | SU3xxx | 1 | 3 MiB | BGA956 | 5.5 W |

| Penryn-3M | Core 2 Duo | SU7xxx | 2 | 3 MB | BGA956 | 10 W |

| SU9xxx | ||||||

| Penryn | SL9xxx | 6 MiB | 17 W | |||

| SP9xxx | 25/28 W | |||||

| Penryn-3M | P7xxx | 3 MiB | Socket P FCBGA6 | 25 W | ||

| P8xxx | ||||||

| Penryn | P9xxx | 6 MiB | ||||

| Penryn-3M | T6xxx | 2 MiB | 35 W | |||

| T8xxx | 3 MiB | |||||

| Penryn | T9xxx | 6 MiB | ||||

| E8x35 | 6 MiB | Socket P | 35-55 W | |||

| Penryn-QC | Core 2 Quad | Q9xxx | 4 | 2x3-2x6 MiB | Socket P | 45 W |

| Penryn XE | Core 2 Extreme | X9xxx | 2 | 6 MiB | Socket P | 44 W |

| Penryn-QC | QX9xxx | 4 | 2x6 MiB | 45 W | ||

| Penryn-3M | Celeron | T3xxx | 2 | 1 MiB | Socket P | 35 W |

| SU2xxx | µFC-BGA 956 | 10 W | ||||

| Penryn-L | 9x0 | 1 | 1 MiB | Socket P | 35 W | |

| 7x3 | µFC-BGA 956 | 10 W | ||||

| Penryn-3M | Pentium | T4xxx | 2 | 1 MiB | Socket P | 35 W |

| SU4xxx | 2 MiB | µFC-BGA 956 | 10 W | |||

| Penryn-L | SU2xxx | 1 | 5.5 W | |||

| Wolfdale-3M | ||||||

| Celeron | E3xxx | 2 | 1 MB | LGA 775 | 65 W | |

| Pentium | E2210 | |||||

| E5xxx | 2 MB | |||||

| E6xxx | ||||||

| Core 2 Duo | E7xxx | 3 MB | ||||

| Wolfdale | E8xxx | 6 MB | ||||

| Xeon | 31x0 | 45-65 W | ||||

| Wolfdale-CL | 30x4 | 1 | LGA 771 | 30 W | ||

| 31x3 | 2 | 65 W | ||||

| Yorkfield | Xeon | X33x0 | 4 | 2×3–2×6 MB | LGA 775 | 65–95 W |

| Yorkfield-CL | X33x3 | LGA 771 | 80 W | |||

| Yorkfield-6M | Core 2 Quad | Q8xxx | 2×2 MB | LGA 775 | 65–95 W | |

| Q9x0x | 2×3 MB | |||||

| Yorkfield | Q9x5x | 2×6 MB | ||||

| Yorkfield XE | Core 2 Extreme | QX9xxx | 2×6 MB | 130–136 W | ||

| QX9xx5 | LGA 771 | 150 W | ||||

| Wolfdale-DP | Xeon | E52xx | 2 | 6 MB | LGA 771 | 65 W |

| L52xx | 20-55 W | |||||

| X52xx | 80 W | |||||

| Harpertown | E54xx | 4 | 2×6 MB | LGA 771 | 80 W | |

| L54xx | 40-50 W | |||||

| X54xx | 120-150 W |

Dunnington

The Xeon "Dunnington" processor (CPUID Family 6, model 29) is closely related to Wolfdale but comes with six cores and an on-chip L3 cache and is designed for servers with Socket 604, so it is marketed only as Xeon, not as Core 2.

| Processor | Brand name | Model (list) | Cores | L3 cache | Socket | TDP |

|---|---|---|---|---|---|---|

| Dunnington | Xeon | E74xx | 4-6 | 8-16 MB | Socket 604 | 90 W |

| L74xx | 4-6 | 12 MB | 50-65 W | |||

| X7460 | 6 | 16 MB | 130 W |

Steppings

The Core microarchitecture uses several stepping levels (steppings), which unlike prior microarchitectures, represent incremental improvements, and different sets of features like cache size and low power modes. Most of these steppings are used across brands, typically by disabling some features and limiting clock frequencies on low-end chips.

Steppings with a reduced cache size use a separate naming scheme, which means that the releases are no longer in alphabetic order. Added steppings have been used in internal and engineering samples, but are unlisted in the tables.

Many of the high-end Core 2 and Xeon processors use Multi-chip modules of two or three chips in order to get larger cache sizes or more than two cores.

Steppings using 65 nm process

| Mobile (Merom) | Desktop (Conroe) | Desktop (Kentsfield) | Server (Woodcrest, Clovertown, Tigerton) | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Stepping | Released | Area | CPUID | L2 cache | Max. clock | Celeron | Pentium | Core 2 | Celeron | Pentium | Core 2 | Xeon | Core 2 | Xeon | Xeon |

| B2 | Jul 2006 | 143 mm² | 06F6 | 4 MiB | 2.93 GHz | M5xx | T5000 T7000 L7000 | E6000 X6000 | 3000 | 5100 | |||||

| B3 | Nov 2006 | 143 mm² | 06F7 | 4 MiB | 3.00 GHz | Q6000 QX6000 | 3200 | 5300 | |||||||

| L2 | Jan 2007 | 111 mm² | 06F2 | 2 MiB | 2.13 GHz | T5000 U7000 | E2000 | E4000 E6000 | 3000 | ||||||

| E1 | May 2007 | 143 mm² | 06FA | 4 MiB | 2.80 GHz | M5xx | T7000 L7000 X7000 | ||||||||

| G0 | Apr 2007 | 143 mm² | 06FB | 4 MiB | 3.00 GHz | M5xx | T7000 L7000 X7000 | E2000 | E4000 E6000 | 3000 | Q6000 QX6000 | 3200 | 5100 5300 7200 7300 | ||

| G2 | Mar 2009 | 143 mm² | 06FB | 4 MiB | 2.16 GHz | M5xx | T5000 T7000 L7000 | ||||||||

| M0 | Jul 2007 | 111 mm² | 06FD | 2 MiB | 2.40 GHz | 5xx T1000 | T2000 T3000 | T5000 T7000 U7000 | E1000 | E2000 | E4000 | ||||

| A1 | Jun 2007 | 81 mm² | 10661 | 1 MiB | 2.20 GHz | M5xx | U2000 | 220 4x0 | |||||||

Early ES/QS steppings are: B0 (CPUID 6F4h), B1 (6F5h) and E0 (6F9h).

Steppings B2/B3, E1, and G0 of model 15 (cpuid 06fx) processors are evolutionary steps of the standard Merom/Conroe die with 4 MiB L2 cache, with the short-lived E1 stepping only being used in mobile processors. Stepping L2 and M0 are the Allendale chips with just 2 MiB L2 cache, reducing production cost and power consumption for low-end processors.

The G0 and M0 steppings improve idle power consumption in C1E state and add the C2E state in desktop processors. In mobile processors, all of which support C1 through C4 idle states, steppings E1, G0, and M0 add support for the Mobile Intel 965 Express (Santa Rosa) platform with Socket P, while the earlier B2 and L2 steppings only appear for the Socket M based Mobile Intel 945 Express (Napa refresh) platform.

The model 22 stepping A1 (cpuid 10661h) marks a significant design change, with just a single core and 1 MiB L2 cache further reducing the power consumption and manufacturing cost for the low-end. Like the earlier steppings, A1 is not used with the Mobile Intel 965 Express platform.

Steppings G0, M0 and A1 mostly replaced all older steppings in 2008. In 2009, a new stepping G2 was introduced to replace the original stepping B2.[7]

Steppings using 45 nm process

| Mobile (Penryn) | Desktop (Wolfdale) | Desktop (Yorkfield) | Server (Wolfdale-DP, Harpertown, Dunnington) | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Stepping | Released | Area | CPUID | L2 cache | Max. clock | Celeron | Pentium | Core 2 | Celeron | Pentium | Core 2 | Xeon | Core 2 | Xeon | Xeon |

| C0 | Nov 2007 | 107 mm² | 10676 | 6 MiB | 3.00 GHz | E8000 P7000 T8000 T9000 P9000 SP9000 SL9000 X9000 | E8000 | 3100 | QX9000 | 5200 5400 | |||||

| M0 | Mar 2008 | 82 mm² | 10676 | 3 MiB | 2.40 GHz | 7xx | SU3000 P7000 P8000 T8000 SU9000 | E5000 E2000 | E7000 | ||||||

| C1 | Mar 2008 | 107 mm² | 10677 | 6 MiB | 3.20 GHz | Q9000 QX9000 | 3300 | ||||||||

| M1 | Mar 2008 | 82 mm² | 10677 | 3 MiB | 2.50 GHz | Q8000 Q9000 | 3300 | ||||||||

| E0 | Aug 2008 | 107 mm² | 1067A | 6 MiB | 3.33 GHz | T9000 P9000 SP9000 SL9000 Q9000 QX9000 | E8000 | 3100 | Q9000 Q9000S QX9000 | 3300 | 5200 5400 | ||||

| R0 | Aug 2008 | 82 mm² | 1067A | 3 MiB | 2.93 GHz | 7xx 900 SU2000 T3000 | T4000 SU2000 SU4000 | SU3000 T6000 SU7000 P8000 SU9000 | E3000 | E5000 E6000 | E7000 | Q8000 Q8000S Q9000 Q9000S | 3300 | ||

| A1 | Sep 2008 | 503 mm² | 106D1 | 3 MiB | 2.67 GHz | 7400 | |||||||||

In the model 23 (cpuid 01067xh), Intel started marketing stepping with full (6 MiB) and reduced (3 MiB) L2 cache at the same time, and giving them identical cpuid values. All steppings have the new SSE4.1 instructions. Stepping C1/M1 was a bug fix version of C0/M0 specifically for quad core processors and only used in those. Stepping E0/R0 adds two new instructions (XSAVE/XRSTOR) and replaces all earlier steppings.

In mobile processors, stepping C0/M0 is only used in the Intel Mobile 965 Express (Santa Rosa refresh) platform, whereas stepping E0/R0 supports the later Intel Mobile 4 Express (Montevina) platform.

Model 30 stepping A1 (cpuid 106d1h) adds an L3 cache and six instead of the usual two cores, which leads to an unusually large die size of 503 mm².[8] As of February 2008, it has only found its way into the very high-end Xeon 7400 series (Dunnington).

System requirements

Motherboard compatibility

Conroe, Conroe XE and Allendale all use Socket LGA 775; however, not every motherboard is compatible with these processors.

Supporting chipsets are:

- Intel: 865G/PE/P, 945G/GZ/GC/P/PL, 965G/P, 975X, P/G/Q965, Q963, 946GZ/PL, P3x, G3x, Q3x, X38, X48, P4x, 5400 Express See also: List of Intel chipsets

- NVIDIA: nForce4 Ultra/SLI X16 for Intel, nForce 570/590 SLI for Intel, nForce 650i Ultra/650i SLI/680i LT SLI/680i SLI and nForce 750i SLI/780i SLI/790i SLI/790i Ultra SLI.

- VIA: P4M800, P4M800PRO, P4M890, P4M900, PT880 Pro/Ultra, PT890. See also: List of VIA chipsets

- SiS: 662, 671, 671fx, 672, 672fx

- ATI: Radeon Xpress 200 and CrossFire Xpress 3200 for Intel

The Yorkfield XE model QX9770 (45 nm with 1600 MT/s FSB) has limited chipset compatibility - with only X38, P35 (With Overclocking) and some high-performance X48 and P45 motherboards being compatible. BIOS updates were gradually being released to provide support for the Penryn technology, and the QX9775 is only compatible with the Intel D5400XS motherboard. The Wolfdale-3M model E7200 also has limited compatibility (at least the Xpress 200 chipset is incompatible).

Although a motherboard may have the required chipset to support Conroe, some motherboards based on the above-mentioned chipsets do not support Conroe. This is because all Conroe-based processors require a new power delivery feature set specified in Voltage Regulator-Down (VRD) 11.0. This requirement is a result of Conroe's significantly lower power consumption, compared to the Pentium 4/D CPUs it replaced. A motherboard that has both a supporting chipset and VRD 11 supports Conroe processors, but even then some boards will need an updated BIOS to recognize Conroe's FID (Frequency ID) and VID (Voltage ID).

Synchronous memory modules

Unlike the prior Pentium 4 and Pentium D design, the Core 2 technology sees a greater benefit from memory running synchronously with the front-side bus (FSB). This means that for the Conroe CPUs with FSB of 1066 MT/s, the ideal memory performance for DDR2 is PC2-8500. In a few configurations, using PC2-5300 instead of PC2-4200 can actually decrease performance. Only when going to PC2-6400 is there a significant performance increase. While DDR2 memory models with tighter timing specifications do improve performance, the difference in real world games and applications is often negligible.[9]

Optimally, the memory bandwidth afforded should match the bandwidth of the FSB, that is to say that a CPU with a 533 MT/s rated bus speed should be paired with RAM matching the same rated speed, for example DDR2 533, or PC2-4200. A common myth is that installing interleaved RAM will offer double the bandwidth. However, at most the increase in bandwidth by installing interleaved RAM is roughly 5–10%. The AGTL+ PSB used by all NetBurst processors and current and medium-term (pre-QuickPath) Core 2 processors provide a 64-bit data path. Current chipsets provide for a couple of either DDR2 or DDR3 channels.

| Processor model | Front-side bus | Matched memory and maximum bandwidth single channel, dual channel | ||

|---|---|---|---|---|

| DDR | DDR2 | DDR3 | ||

| Mobile: T5200, T5300, U2n00, U7n00 | 533 MT/s | PC-3200 (DDR-400) 3.2 GB/s |

PC2-4200 (DDR2-533) 4.264 GB/s PC2-8500 (DDR2-1066) 8.532 GB/s |

PC3-8500 (DDR3-1066) 8.530 GB/s |

| Desktop: E6n00, E6n20, X6n00, E7n00, Q6n00 and QX6n00 Mobile: T9400, T9550, T9600, P7350, P7450, P8400, P8600, P8700, P9500, P9600, SP9300, SP9400, X9100 |

1066 MT/s | |||

| Mobile: T5n00, T5n50, T7n00 (Socket M), L7200, L7400 | 667 MT/s | PC-3200 (DDR-400) 3.2 GB/s |

PC2-5300 (DDR2-667) 5.336 GB/s |

PC3-10600 (DDR3-1333) 10.670 GB/s |

| Desktop: E6n40, E6n50, E8nn0, Q9nn0, QX6n50, QX9650 | 1333 MT/s | |||

| Mobile: T5n70, T6400, T7n00 (Socket P), L7300, L7500, X7n00, T8n00, T9300, T9500, X9000 Desktop: E4n00, Pentium E2nn0, Pentium E5nn0, Celeron 4n0, E3n00 |

800 MT/s | PC-3200 (DDR-400) 3.2 GB/s PC-3200 (DDR-400) 3.2 GB/s |

PC2-6400 (DDR2-800) 6.400 GB/s PC2-8500 (DDR2-1066) 8.532 GB/s |

PC3-6400 (DDR3-800) 6.400 GB/s PC3-12800 (DDR3-1600) 12.800 GB/s |

| Desktop: QX9770, QX9775 | 1600 MT/s | |||

On jobs requiring large amounts of memory access, the quad-core Core 2 processors can benefit significantly[10] from using PC2-8500 memory, which runs at the same speed as the CPU's FSB; this is not an officially supported configuration, but several motherboards support it.

The Core 2 processor does not require the use of DDR2. While the Intel 975X and P965 chipsets require this memory, some motherboards and chipsets support both Core 2 processors and DDR memory. When using DDR memory, performance may be reduced because of the lower available memory bandwidth.

Chip errata

The Core 2 memory management unit (MMU) in X6800, E6000 and E4000 processors does not operate to prior specifications implemented in prior generations of x86 hardware. This may cause problems, many of them serious security and stability issues, with extant operating system software. Intel's documentation states that their programming manuals will be updated "in the coming months" with information on recommended methods of managing the translation lookaside buffer (TLB) for Core 2 to avoid issues, and admits that, "in rare instances, improper TLB invalidation may result in unpredictable system behavior, such as hangs or incorrect data."[11]

Among the issues stated:

- Non-execute bit is shared across the cores.

- Floating point instruction non-coherencies.

- Allowed memory corruptions outside of the range of permitted writing for a process by running common instruction sequences.

Intel errata Ax39, Ax43, Ax65, Ax79, Ax90, Ax99 are said to be particularly serious.[12] 39, 43, 79, which can cause unpredictable behavior or system hang, have been fixed in recent steppings.

Among those who have stated the errata to be particularly serious are OpenBSD's Theo de Raadt[13] and DragonFly BSD's Matthew Dillon.[14] Taking a contrasting view was Linus Torvalds, calling the TLB issue "totally insignificant", adding, "The biggest problem is that Intel should just have documented the TLB behavior better."[15]

Microsoft has issued update KB936357 to address the errata by microcode update,[16] with no performance penalty. BIOS updates are also available to fix the issue.

References

- "Penryn Arrives: Core 2 Extreme QX9650 Review". ExtremeTech. Archived from the original on October 31, 2007. Retrieved October 30, 2006.

- King, Ian (April 9, 2007). "How Israel saved Intel". The Seattle Times. Retrieved April 15, 2012.

- Swinburne, Richard (November 3, 2008). "Intel Core i7 – Nehalem Architecture Dive: 5 – Architecture Enhancements". Retrieved August 21, 2011.

- "Intel Xeon Processor 5110". Intel. Retrieved April 15, 2012.

- "Intel Xeon Processor 5120". Intel. Retrieved April 15, 2012.

- http://www.anandtech.com/show/2362

- "Product Change Notice" (PDF). Archived from the original (PDF) on December 22, 2010. Retrieved June 17, 2012.

- "ARK entry for Intel Xeon Processor X7460". Intel. Retrieved July 14, 2009.

- piotke (August 1, 2006). "Intel Core 2: Is high speed memory worth its price?". Madshrimps. Retrieved August 1, 2006.

- Jacob (May 19, 2007). "Benchmarks of four Prime95 processes on a quad-core". Mersenne Forum. Retrieved May 22, 2007.

- "Dual-Core Intel Xeon Processor 7200 Series and Quad-Core Intel Xeon Processor 7300 Series" (PDF). p. 46. Retrieved January 23, 2010.

- "Intel Core 2 Duo Processor for Intel Centrino Duo Processor Technology Specification Update" (PDF). pp. 18–21.

- marc.info

- "Matthew Dillon on Intel Core Bugs". OpenBSD journal. June 30, 2007. Retrieved April 15, 2012.

- Torvalds, Linus (June 27, 2007). "Core 2 Errata -- problematic or overblown?". Real World Technologies. Retrieved April 15, 2012.

- "A microcode reliability update is available that improves the reliability of systems that use Intel processors". Microsoft. October 8, 2011. Retrieved April 15, 2012.

External links

- Intel Core Microarchitecture website

- Intel press release announcing plans for a new microarchitecture

- Intel press release introducing the Core Microarchitecture

- Intel processor roadmap

- A Detailed Look at Intel's New Core Architecture

- Intel names the Core Microarchitecture

- Pictures of processors using the Core Microarchitecture, among others (also first mention of Clovertown-MP)

- IDF keynotes, advertising the performance of the new processors

- The Core of Intel's new chips

- RealWorld Tech's overview of the Core microarchitecture

- Detailed overview of the Core microarchitecture at Ars Technica

- Intel Core versus AMD's K8 architecture at Anandtech

- Release dates of upcoming Intel Core processors using the Intel Core Microarchitecture

- Benchmarks Comparing the Computational Power of Core Architecture against Older Intel Netburst and AMD Athlon64 Central Processing Units