QorIQ

QorIQ /ˈkɔːraɪkjuː/ is a brand of ARM-based and Power ISA-based communications microprocessors from NXP Semiconductors (formerly Freescale). It is the evolutionary step from the PowerQUICC platform, and initial products were built around one or more e500mc cores and came in five different product platforms, P1, P2, P3, P4, and P5, segmented by performance and functionality. The platform keeps software compatibility with older PowerPC products such as the PowerQUICC platform. In 2012 Freescale announced ARM-based QorIQ offerings beginning in 2013.[1]

| POWER, PowerPC, and Power ISA architectures |

|---|

| NXP (formerly Freescale and Motorola) |

| IBM |

|

| IBM/Nintendo |

| Other |

| Related links |

|

| Cancelled in gray, historic in italic |

The QorIQ brand and the P1, P2 and P4 product families were announced in June 2008. Details of P3 and P5 products were announced in 2010.

QorIQ P Series processors were manufactured on a 45 nm fabrication process and was available in the end of 2008 (P1 and P2), mid-2009 (P4) and 2010 (P5).

QorIQ T Series is based on a 28 nm process and is pushing a very aggressive power envelope target, capping at 30 W. These are using the e6500 core with AltiVec and are expected to be shipping in 2013.

QorIQ LS-1 and LS-2 families are ARM based processors using the Cortex A7, Cortex A9, A15, A53 and A72 cores upon the ISA agnostic Layerscape architecture. They are available since 2013 and target low and mid range networking and wireless infrastructure applications.[1]

Layerscape

The Layerscape (LS) architecture is the latest evolution of the QorIQ family, in that features previously provided by DPAA (like compression) may be implemented in software or hardware, depending on the specific chip, but transparent to application programmers. LS-1 and LS-2 are announced to use Cortex A7, A9, A15, A53 and A72 cores.[1]

The initial LS-1 series does not include any accelerated packet processing layer, focusing typical power consumption of less than 3W using two Cortex A7 with providing ECC for caches and DDR3/4 at 1000 to 1600 MT/s, dual PCI Express Controllers in x1/x2/x4 operation, SD/MMC, SATA 1/2/3, USB 2/3 with integrated PHY, and virtualized eTSEC Gigabit Ethernet Controllers.[2]

LS1 means LS1XXX series (e.g., LS1021A, etc.); LS2 means LS2XXX series. LS2 means a higher performance level than LS1, and it does not indicate a second generation. The middle two digits of the product name are core count; the last digit distinguishes models, with, in most but not all cases, a higher digit meaning greater performance. “A” at the end indicates the Arm processor. LX designates the 16 nm FinFET generation.

The LS1 family is built on the Layerscape architecture is a programmable data-plane engine networking architecture. Both LS1 and LS2 families of processors offer the advanced, high-performance datapath and network peripheral interfaces. These features are frequently required for networking, telecom/datacom, wireless infrastructure, military and aerospace applications.

Initial announcement

Freescale Semiconductor Inc. (acquired by NXP Semiconductors in late 2015) announced a network processor system architecture said to give the flexibility and scalability required by network infrastructure OEMs to handle the market trends of connected devices, massive datasets, tight security, real-time service and increasingly unpredictable network traffic patterns.[3][4][5]

Layerscape product family list

| Security | ||||||||

| Device | Cores | Frequency | PCIe | SerDES | SATA | Integrated SEC

Engine |

DCE/PME | QUICC Engine |

|---|---|---|---|---|---|---|---|---|

| LS1012A | 1 x ARM Cortex-A53 | 1.0 GHz | 1 x Gen2.0 | 3 lanes 6 GHz | Yes | Yes | - | - |

| LS1020A | 2 x ARM Cortex-A7 | 1.2 GHz | 2 x Gen2.0 | 4 lanes 6 GHz | Yes | Yes | - | Yes |

| LS1021A | 2 x ARM Cortex-A7 | 1.2 GHz | 2 x Gen2.0 | 4 lanes 6 GHz | Yes | Yes | - | Yes |

| LS1022A | 2 x ARM Cortex-A7 | 0.6 GHz | 1 x Gen2.0 | 1 lane 5 GHz | No | Yes | - | - |

| LS1024A | 2 x ARM Cortex-A9 | 1.2 GHz | 2 x Gen2.0 | 3 lanes 5 GHz | Yes | Yes | Yes | - |

| LS1028A | 2 x ARM Cortex-A72 | 1.3 GHz | 2 x Gen2.0 | 4 lanes 10 GHz | Yes | Yes | - | - |

| LS1043A | 4 x ARM Cortex-A53 | 1.6 GHz | 3 x Gen2.0 | 4 lanes 10 GHz | Yes | Yes | - | Yes |

| LA1575 | 2 x ARM Cortex-A53 | 1.4 GHz | 1 x Gen3.0 | 4 lanes 10 GHz | Yes | Yes | - | - |

| LS1046A | 4 x ARM Cortex-A72 | 1.8 GHz | 3 x Gen3.0 | 8 lanes 10 GHz | Yes | Yes | - | - |

| LS1088A | 8 x ARM Cortex-A53 | 1.6 GHz | 3 x Gen3.0 | 4 lanes 10 GHz | Yes | Yes | - | Yes |

| LX2160A | 16 x ARM Cortex-A72 | 2.2 GHz | 6x Gen 4.0 | 24 lanes 25 GHz | Yes | Yes | 100 Gbps | |

P Series

The QorIQ P Series processors are based on e500 or e5500 cores. The P10xx series, P2010 and P2020 are based on the e500v2 core, P204x, P30xx and P40xx on the e500mc core, and P50xx on the e5500 core. Features include 32/32 kB data/instruction L1 cache, 36-bit physical memory addressing [appended to the top of the virtual address in the process context, each process is still 32bit], a double precision floating point unit is present on some cores (not all) and support for virtualization through a hypervisor layer is present in products featuring the e500mc or the e5500. The dual and multi-core devices supports both symmetric and asymmetric multiprocessing, and can run multiple operating systems in parallel.

P1

The P1 series is tailored for gateways, Ethernet switches, wireless LAN access points, and general-purpose control applications. It is the entry level platform, ranging from 400 to 800 MHz devices. It is designed to replace the PowerQUICC II Pro and PowerQUICC III platforms. The chips include among other integrated functionality, Gigabit Ethernet controllers, two USB 2.0 controllers, a security engine, a 32-bit DDR2 and DDR3 memory controller with ECC support, dual four-channel DMA controllers, a SD/MMC host controller and high speed interfaces which can be configured as SerDes lanes, PCIe and SGMII interfaces. The chip is packaged in 689-pin packages which are pin compatible with the P2 family processors.[6][7]

- P1011 – Includes one 800 MHz e500 core, 256 kB L2 cache, four SerDes lanes, three Gbit Ethernet controllers and a TDM engine for legacy phone applications.

- P1020 – includes two 800 MHz e500 cores, 256 kB shared L2 cache, four SerDes lanes, three Gbit Ethernet controllers and a TDM engine.

P2

The P2 series is designed for a wide variety of applications in the networking, telecom, military and industrial markets. It will be available in special high quality parts, with junction tolerances from −40 to 125 °C, especially suited for demanding out doors environments. It is the mid-level platform, with devices ranging from 800 MHz up to 1.2 GHz. It is designed to replace the PowerQUICC II Pro and PowerQUICC III platforms. The chips include, among other integrated functionality, a 512 kB L2 cache, a security engine, three Gigabit Ethernet controllers, a USB 2.0 controller, a 64-bit DDR2 and DDR3 memory controller with ECC support, dual four-channel DMA controllers, a SD/MMC host controller and high speed SerDes lanes which can be configured as three PCIe interfaces, two RapidIO interfaces and two SGMII interfaces. The chips are packaged in 689-pin packages which are pin compatible with the P1 family processors.[6][8]

- P2010 – Includes one 1.2 GHz core

- P2020 – Includes two 1.2 GHz cores, with shared L2 cache

P3

The P3 series is a mid performance networking platform, designed for switching and routing. The P3 family offers a multi-core platform, with support for up to four e500mc cores at frequencies up to 1.5 GHz on the same chip, connected by the CoreNet coherency fabric. The chips include among other integrated functionality, integrated L3 caches, memory controller, multiple I/O-devices such as DUART, GPIO and USB 2.0, security and encryption engines, a queue manager scheduling on-chip events and a SerDes based on-chip high speed network configurable as multiple Gigabit Ethernet, 10 Gigabit Ethernet, RapidIO or PCIe interfaces.[9]

The P3 family processors share the same physical package with, and are also software backwards compatible with, P4 and P5. The P3 processors have 1.3 GHz 64-bit DDR3 memory controllers, 18 SerDes lanes for networking, hardware accelerators for packet handling and scheduling, regular expressions, RAID, security, cryptography and RapidIO.

The cores are supported by a hardware hypervisor and can be run in symmetric or asymmetric mode meaning that the cores can run and boot operating systems together or separately, resetting and partitioning cores and datapaths independently without disturbing other operating systems and applications.

- P2040

- P2041

- P3041 – Quad 1.5 GHz cores, 128 kB L2 cache per core, single 1.3 GHz 64-bit DDR3 controller. Manufactured on a 45 nm process operating in a 12W envelope.

P4

The P4 series is a high performance networking platform, designed for backbone networking and enterprise level switching and routing. The P4 family offers an extreme multi-core platform, with support for up to eight e500mc cores at frequencies up to 1.5 GHz on the same chip, connected by the CoreNet coherency fabric. The chips include among other integrated functionality, integrated L3 caches, memory controllers, multiple I/O-devices such as DUART, GPIO and USB 2.0, security and encryption engines, a queue manager scheduling on-chip events and a SerDes based on-chip high speed network configurable as multiple Gigabit Ethernet, 10 Gigabit Ethernet, RapidIO or PCIe interfaces.

The cores are supported by a hardware hypervisor and can be run in symmetric or asymmetric mode meaning that the cores can run and boot operating systems together or separately, resetting and partitioning cores and datapaths independently without disturbing other operating systems and applications.

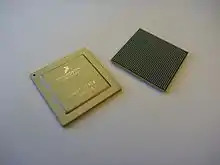

- P4080 – Includes eight e500mc cores, each with 32/32kB instruction/data L1 caches and a 128 kB L2 cache. The chip has dual 1 MB L3 caches, each connected to a 64-bit DDR2/DDR3 memory controller. The chip contains a security and encryption module, capable of packet parsing and classification, and acceleration of encryption and regexp pattern matching. The chip can be configured with up to eight Gigabit and two 10 Gigabit Ethernet controllers, three 5 GHz PCIe ports and two RapidIO interfaces. It also has various other peripheral connectivity such as two USB2 controllers. It is designed to operate below 30 W at 1.5 GHz. The processor is manufactured on a 45 nm SOI process and begun sampling to customers in August 2009.[10]

To help software developers and system designers get started with the QorIQ P4080, Freescale worked with Virtutech to create a virtual platform for the P4080 that can be used prior to silicon availability to develop, test, and debug software for the chip. Currently, the simulator is only for the P4080, not the other chips announced in 2008.[11]

Because of its complete set of network engines, this processor can be used for telecommunication systems (LTE eNodeB, EPC, WCDMA, BTS), so Freescale and 6WIND ported 6WIND's packet processing software to the P4080.[12][13]

P5

The P5 series is based on the high performance 64-bit e5500 core scaling up to 2.5 GHz and allowing numerous auxiliary application processing units as well as multi core operation via the CoreNet fabric. The P5 series processors share the same physical package and are also software backwards compatible with P3 and P4. The P5 processors have 1.3 GHz 64-bit DDR3 memory controllers, 18 SerDes lanes for networking, hardware accelerators for packet handling and scheduling, regular expressions, RAID, security, cryptography and RapidIO.

Introduced in June 2010, samples will be available late 2010 and full production is expected in 2011.

Applications range from high end networking control plane infrastructure, high end storage networking and complex military and industrial devices.

- P5010 – Single e5500 2.2 GHz core, 1 MB L3 cache, single 1.333 lGHz DDR3 controller, manufactured on a 45 nm process and operating in a 30W envelope.

- P5020 – Dual e5500 2.2 GHz cores, dual 1 MB L3 caches, dual 1.333 lGHz DDR3 controllers, manufactured on a 45 nm process and operating in a 30W envelope.

- P5021 – Dual e5500 2.4 GHz cores, 1.6 GHz DDR3/3L. Sampling since March 2012; production expected in 4Q12.

- P5040 – Quad e5500 2.4 GHz cores, 1.6 GHz DDR3/3L. Sampling since March 2012; production expected in 4Q12.

Qonverge

In February 2011 Freescale introduced the QorIQ Qonverge platform which is a series of combined CPU and DSP SoC processors targeting wireless infrastructure applications.[14] The PSC913x family chips uses an e500 core based CPU and StarCore SC3850 DSPs will be available in 2011, and is manufactured on a 45 nm process, with e6500 and CS3900 core based 28 nm parts available in 2012 called P4xxx.

AMP Series

The QorIQ Advanced Multiprocessing, AMP Series, processors are all based on the multithreaded 64-bit e6500 core with integrated AltiVec SIMD processing units except the lowest end T1 family that uses the older e5500 core. Products will range from single core versions up to parts with 12 cores or more with frequencies ranging all the way up to 2.5 GHz. The processes will be sectioned into five classes according to performance and features, named T1 through T5, and will be manufactured in a 28 nm process beginning in 2012.[15]

T4

The T4 family uses the e6500 64-bit dual threaded core.

- T4240 – The first product announced and incorporates twelve cores, three memory controllers and various other accelerators.[16]

- T4160 – A feature reduced version of the T4240 with only eight cores, and less I/O options and just two memory controllers.[16]

- T4080 – A feature reduced version of the T4240 with only four cores, and less I/O options and just two memory controllers.[16]

T2

The T2 family uses the e6500 64-bit dual threaded core.

- T2080 and T2081 – Processors with four cores running at speeds of 1.5 to 1.8 GHz. The '81 parts comes in smaller package, slightly different I/O options and therefore fewer I/O pins.[17] The T2081 is pin compatible with the lower end T104x and T102x parts.

T1

The T1 family uses the e5500 64-bit single threaded core at 1.2 to 1.5 GHz with 256 kB L2 cache per core and 256kB shared CoreNet L3 cache.

- T1040 – Quad-core, four Gbit Ethernet ports and an 8 port Ethernet switch

- T1042 – Quad-core, five Gbit Ethernet ports, no Ethernet switch.

- T1020 – Dual-core, four Gbit Ethernet ports and an 8 port Ethernet switch

- T1022 – Dual-core, five Gbit Ethernet ports, no Ethernet switch.

System design

Networking, IT and telecommunication systems

The QorIQ products bring some new challenges in order to design some control planes of telecommunication systems and their data plane. For instance, when 4 or 8 cores are used, such as the P4080, in order to achieve millions of Packet Processing per seconds, the system does not scale with regular software stack because so many cores require a different system design.[18] In order to restore simplicity and still get the highest level of performance, the telecommunication systems are based on a segregation of the cores. Some cores are used for the control plane while some others are used for a re-designed data plane based on a Fast Path.

Freescale has partnered with networking company 6WIND to provide software developers with a high-performance commercial packet processing solution for the QorIQ platform.[19]

See also

References

- Freescale adopts ARM cores in QorIQ line

- Nov 2012: Layercape – New Embedded Family Solution

- Hogg, Scott. "6 network and security trends you can expect in 2017". Network World. Retrieved 2018-04-23.

- Newman, Daniel. "The Top 8 IoT Trends For 2018". Forbes. Retrieved 2018-04-23.

- D. Mistry, P. Modi, K. Deokule, A. Patel, H. Patki and O. Abuzaghleh, "Network traffic measurement and analysis," 2016 IEEE Long Island Systems, Applications and Technology Conference (LISAT), Farmingdale, NY, 2016, pp. 1–7.

- Freescale announces pin-compatible, power-efficient series in new QorIQ communications platforms – businesswire.com

- P1 Series Single- and Dual-Core Communications Processors – Freescale.com

- P2 Series Single- and dual-core communications processors – Freescale.com

- http://cache.freescale.com/files/32bit/doc/fact_sheet/QP3041FS.pdf?fpsp=1&WT_TYPE=Fact%20Sheets&WT_VENDOR=FREESCALE&WT_FILE_FORMAT=pdf&WT_ASSET=Documentation

- P4 Series P4080 multicore processor – Freescale.com

- Virtutech page about P4080 simulation support

- 6WIND

- 6WIND's packet processing software

- Freescale introduces industry's first multimode wireless base station processor family that scales from small to large cells, Businesswire.com

- "Freescale Drives Embedded Multicore Innovation with New QorIQ Advanced Multiprocessing Series". Freescale. 2011-06-21. Archived from the original on 2012-07-17. Retrieved 2011-07-12.

- T4240: QorIQ T Series T4240/T4160 24/16 Virtual Core Communications Processors

- T2080: QorIQ T Series T2080/T2081 Eight Virtual Core Communications Processors

- "regular software stack". Archived from the original on 2012-11-12. Retrieved 2009-10-23.

- http://www.6wind.com/wp-content/uploads/PDF/press/2010/6WIND_Software_Provides_10x_the_Performance.pdf

External links

- NXP Semiconductors QorIQ website

- EE Times, NXP Processor Powers IoT, Networks

- Migrating PowerQUICC® III Processors to QorIQ™ Platforms

- QorIQ 45-nm communications MPUs feature dual cores, low power – ElectronicProducts.com

- MontaVista Provides First No-Cost Evaluation of Commercial Linux for Freescale QorIQ P4080 Multicore Processor – Money.AOL.com