90 nm process

The 90 nm process refers to the level of MOSFET (CMOS) fabrication process technology that was commercialized by the 2003–2005 timeframe, by leading semiconductor companies like Toshiba, Sony, Samsung, IBM, Intel, Fujitsu, TSMC, Elpida, AMD, Infineon, Texas Instruments and Micron Technology.

| Semiconductor device fabrication |

|---|

|

|

(process nodes) |

The origin of the 90 nm value is historical, as it reflects a trend of 70% scaling every 2–3 years. The naming is formally determined by the International Technology Roadmap for Semiconductors (ITRS).

The 193 nm wavelength was introduced by many (but not all) companies for lithography of critical layers mainly during the 90 nm node. Yield issues associated with this transition (due to the use of new photoresists) were reflected in the high costs associated with this transition.

Even more significantly, the 300 mm wafer size became mainstream at the 90 nm node. The previous wafer size was 200 mm diameter.

History

A 90 nm silicon MOSFET was fabricated by Iranian engineer Ghavam Shahidi (later IBM director) with D.A. Antoniadis and H.I. Smith at MIT in 1988. The device was fabricated using X-ray lithography.[1]

Toshiba, Sony and Samsung developed a 90 nm process during 2001–2002, before being introduced in 2002 for Toshiba's eDRAM and Samsung's 2 Gb NAND flash memory.[2][3] IBM demonstrated a 90 nm silicon-on-insulator (SOI) CMOS process, with development led by Ghavam Shahidi, in 2002. The same year, Intel demonstrated a 90 nm strained-silicon process.[4] Fujitsu commercially introduced its 90 nm process in 2003[5] followed by TSMC in 2004.[6]

Gurtej Singh Sandhu of Micron Technology initiated the development of atomic layer deposition high-k films for DRAM memory devices. This helped drive cost-effective implementation of semiconductor memory, starting with 90 nm node DRAM.[7]

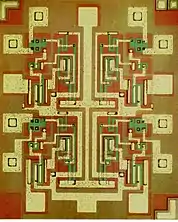

Example: Elpida 90 nm DDR2 SDRAM process

Elpida Memory's 90 nm DDR2 SDRAM process.[8]

- Use of 300 mm wafer size

- Use of KrF (248 nm) lithography with optical proximity correction

- 512 Mbit

- 1.8 V operation

- Derivative of earlier 110 nm and 100 nm processes

Processors using 90 nm process technology

- Sony/Toshiba EE+GS (PlayStation 2) - 2003[9]

- Sony/Toshiba/IBM Cell Processor - 2005

- IBM PowerPC G5 970FX - 2004

- IBM PowerPC G5 970MP - 2005

- IBM PowerPC G5 970GX - 2005

- IBM "Waternoose" Xbox 360 Processor - 2005

- Intel Pentium 4 Prescott - 2004-02

- Intel Celeron D Prescott-256 - 2004-05

- Intel Pentium M Dothan - 2004-05

- Intel Celeron M Dothan-1024 - 2004-08

- Intel Xeon Nocona, Irwindale, Cranford, Potomac, Paxville - 2004-06

- Intel Pentium D Smithfield - 2005-05

- AMD Athlon 64 Winchester, Venice, San Diego, Orleans - 2004-10

- AMD Athlon 64 X2 Manchester, Toledo, Windsor - 2005-05

- AMD Sempron Palermo and Manila - 2004-08

- AMD Turion 64 Lancaster and Richmond - 2005-03

- NVIDIA GeForce 8800 GTS (G80) - 2006

- AMD Turion 64 X2 Taylor and Trinidad - 2006-05

- AMD Opteron Venus, Troy, and Athens - 2005-08

- AMD Dual-core Opteron Denmark, Italy, Egypt, Santa Ana, and Santa Rosa

- VIA C7 - 2005-05

- Loongson (Godson) 2Е STLS2E02 - 2007-04

- Loongson (Godson) 2F STLS2F02 - 2008-07

- MCST-4R - 2010-12

- Elbrus-2S+ - 2011-11

See also

References

- Shahidi, Ghavam G.; Antoniadis, D. A.; Smith, H. I. (December 1988). "Reduction of hot-electron-generated substrate current in sub-100-nm channel length Si MOSFET's". IEEE Transactions on Electron Devices. 35 (12): 2430–. doi:10.1109/16.8835.

- "Toshiba and Sony Make Major Advances in Semiconductor Process Technologies". Toshiba. 3 December 2002. Retrieved 26 June 2019.

- "Our Proud Heritage from 2000 to 2009". Samsung Semiconductor. Samsung. Retrieved 25 June 2019.

- "IBM, Intel wrangle at 90 nm". EE Times. 13 December 2002. Retrieved 17 September 2019.

- 65nm CMOS Process Technology

- "90nm Technology". TSMC. Retrieved 30 June 2019.

- "IEEE Andrew S. Grove Award Recipients". IEEE Andrew S. Grove Award. Institute of Electrical and Electronics Engineers. Retrieved 4 July 2019.

- Elpida's presentation at Via Technology Forum 2005 and Elpida 2005 Annual Report

- "EMOTION ENGINE® AND GRAPHICS SYNTHESIZER USED IN THE CORE OF PLAYSTATION® BECOME ONE CHIP" (PDF). Sony. April 21, 2003. Retrieved 26 June 2019.