3 nm process

In semiconductor manufacturing, the 3 nm process is the next die shrink after the 5-nanometre MOSFET (metal–oxide–semiconductor field-effect transistor) technology node. As of 2019, Intel, Samsung, and TSMC have all announced plans to put a 3 nm semiconductor node into commercial production. Samsung's 3 nm process is based on GAAFET (gate-all-around field-effect transistor) technology, a type of multi-gate MOSFET technology, while TSMC's 3nm process will still use FinFET (fin field-effect transistor) technology,[1] despite TSMC developing GAAFET transistors.[2] Specifically, Samsung plans to use its own variant of GAAFET called MBCFET (multi-bridge channel field-effect transistor).[3]

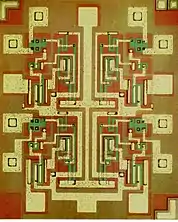

| Semiconductor device fabrication |

|---|

|

|

(process nodes) |

History

Research and technology demos

In 1985, a Nippon Telegraph and Telephone (NTT) research team fabricated a MOSFET (NMOS) device with a channel length of 150 nm and gate oxide thickness of 2.5 nm.[4] In 1998, an Advanced Micro Devices (AMD) research team fabricated a MOSFET (NMOS) device with a channel length of 50 nm and oxide thickness of 1.3 nm.[5][6]

In 2003, a research team at NEC fabricated the first MOSFETs with a channel length of 3 nm, using the PMOS and NMOS processes.[7][8] In 2006, a team from the Korea Advanced Institute of Science and Technology (KAIST) and the National Nano Fab Center, developed a 3 nm width multi-gate MOSFET, the world's smallest nanoelectronic device, based on gate-all-around (GAAFET) technology.[9][10]

Commercialization history

In late 2016, TSMC announced plans to construct a 5 nm–3 nm node semiconductor fabrication plant with a co-commitment investment of around US$15.7 billion.[11]

In 2017, TSMC announced it was to begin construction of the 3 nm semiconductor fabrication plant at the Tainan Science Park in Taiwan.[12] TSMC plans to start volume production of the 3 nm process node in 2023.[13][14][15][16][17]

In early 2018, IMEC and Cadence stated they had taped out 3 nm test chips, using extreme ultraviolet lithography (EUV) and 193 nm immersion lithography.[18]

In early 2019, Samsung presented plans to manufacture 3 nm GAAFET (gate-all-around field-effect transistors) at the 3 nm node in 2021, using its own MBCFET transistor structure that uses nanosheets instead of nanowires; delivering a 35% performance increase, 50% power reduction and a 45% reduction in area when compared with 7nm.[19][20][21] Samsung's semiconductor roadmap also included products at 8, 7, 6, 5, and 4 nm 'nodes'.[22][23]

In December 2019, Intel announced plans for 3 nm production in 2025.[24]

In January 2020, Samsung announced the production of the world's first 3 nm GAAFET process prototype, and said that it is targeting mass production in 2021.[25]

In August 2020, TSMC announced details of its N3 3nm process, which is new rather than being an improvement over its N5 5nm process.[26] Compared with the N5 process, the N3 process should offer a 10–15% (1.10–1.15×) increase in performance, or a 25–35% (1.25–1.35×) decrease in power consumption, with a 1.7× increase in logic density (a scaling factor of 0.58), a 20% increase (0.8 scaling factor) in SRAM cell density, and a 10% increase in analog circuitry density. Since many designs include considerably more SRAM than logic, (a common ratio being 70% SRAM to 30% logic) die shrinks are expected to only be of around 26%. TSMC plans risk production in 2021 with volume production in the second half of 2022.[27][28][2]

Beyond 3 nm

The ITRS uses (as of 2017) the terms "2.1 nm", "1.5 nm", and "1.0 nm" as generic terms for the nodes after 3 nm.[29][30] "2-nanometre" (2 nm) and "14 angstrom" (14 Å or 1.4 nm) nodes have also been (in 2017) tentatively identified by An Steegen (of IMEC) as future production nodes after 3 nm, with hypothesized introduction dates of around 2024, and beyond 2025 respectively.[31]

In late 2018, TSMC chairman Mark Liu predicted chip scaling would continue to 3 nm and 2 nm nodes;[32] however, as of 2019, other semiconductor specialists were undecided as to whether nodes beyond 3 nm could become viable.[33] TSMC began research on 2 nm in 2019.[34] It has been reported that TSMC is expected to enter 2 nm risk production around 2023 or 2024.[35]

In December 2019, Intel announced plans for 1.4 nm production in 2029.[24]

References

- Cutress, Dr Ian. "Where are my GAA-FETs? TSMC to Stay with FinFET for 3nm". www.anandtech.com.

- "TSMC Plots an Aggressive Course for 3nm Lithography and Beyond - ExtremeTech". www.extremetech.com.

- https://techxplore.com/news/2019-05-samsung-foundry-event-3nm-mbcfet.amp

- Kobayashi, Toshio; Horiguchi, Seiji; Miyake, M.; Oda, M.; Kiuchi, K. (December 1985). "Extremely high transconductance (above 500 mS/mm) MOSFET with 2.5 nm gate oxide". 1985 International Electron Devices Meeting: 761–763. doi:10.1109/IEDM.1985.191088. S2CID 22309664.

- Ahmed, Khaled Z.; Ibok, Effiong E.; Song, Miryeong; Yeap, Geoffrey; Xiang, Qi; Bang, David S.; Lin, Ming-Ren (1998). "Performance and reliability of sub-100 nm MOSFETs with ultra thin direct tunneling gate oxides". 1998 Symposium on VLSI Technology Digest of Technical Papers (Cat. No.98CH36216): 160–161. doi:10.1109/VLSIT.1998.689240. ISBN 0-7803-4770-6. S2CID 109823217.

- Ahmed, Khaled Z.; Ibok, Effiong E.; Song, Miryeong; Yeap, Geoffrey; Xiang, Qi; Bang, David S.; Lin, Ming-Ren (1998). "Sub-100 nm nMOSFETs with direct tunneling thermal, nitrous and nitric oxides". 56th Annual Device Research Conference Digest (Cat. No.98TH8373): 10–11. doi:10.1109/DRC.1998.731099. ISBN 0-7803-4995-4. S2CID 1849364.

- Schwierz, Frank; Wong, Hei; Liou, Juin J. (2010). Nanometer CMOS. Pan Stanford Publishing. p. 17. ISBN 9789814241083.

- Wakabayashi, Hitoshi; Yamagami, Shigeharu; Ikezawa, Nobuyuki; Ogura, Atsushi; Narihiro, Mitsuru; Arai, K.; Ochiai, Y.; Takeuchi, K.; Yamamoto, T.; Mogami, T. (December 2003). "Sub-10-nm planar-bulk-CMOS devices using lateral junction control". IEEE International Electron Devices Meeting 2003: 20.7.1–20.7.3. doi:10.1109/IEDM.2003.1269446. ISBN 0-7803-7872-5. S2CID 2100267.

- "Still Room at the Bottom (nanometer transistor developed by Yang-kyu Choi from the Korea Advanced Institute of Science and Technology )", Nanoparticle News, 1 April 2006, archived from the original on 6 November 2012

- Lee, Hyunjin; Choi, Yang-Kyu; Yu, Lee-Eun; Ryu, Seong-Wan; Han, Jin-Woo; Jeon, K.; Jang, D.Y.; Kim, Kuk-Hwan; Lee, Ju-Hyun; et al. (June 2006), "Sub-5nm All-Around Gate FinFET for Ultimate Scaling", Symposium on VLSI Technology, 2006: 58–59, doi:10.1109/VLSIT.2006.1705215, hdl:10203/698, ISBN 978-1-4244-0005-8

- Patterson, Alan (12 December 2016), "TSMC Plans New Fab for 3nm", www.eetimes.com

- Patterson, Alan (2 October 2017), "TSMC Aims to Build World's First 3-nm Fab", www.eetimes.com

- Zafar, Ramish (15 May 2019), TSMC To Commence 2nm Research In Hsinchu, Taiwan Claims Report

- "TSMC to start production on 5nm in second half of 2020, 3nm in 2022". www.techspot.com.

- Armasu 2019-12-06T20:26:59Z, Lucian. "Report: TSMC To Start 3nm Volume Production In 2022". Tom's Hardware.

- "TSMC 3nm process fab starts construction - mass production in 2023". Gizchina.com. 25 October 2019.

- Friedman, Alan. "TSMC starts constructing facilities to turn out 3nm chips by 2023". Phone Arena.

- "Imec and Cadence Tape Out Industry's First 3nm Test Chip", www.cadence.com (press release), 28 February 2018

- "Samsung Unveils 3nm Gate-All-Around Design Tools - ExtremeTech". www.extremetech.com.

- Armasu, Lucian (11 January 2019), "Samsung Plans Mass Production of 3nm GAAFET Chips in 2021", www.tomshardware.com

- Samsung: 3nm process is one year ahead of TSMC in GAA and three years ahead of Intel, 6 August 2019

- Armasu, Lucian (25 May 2017), "Samsung Reveals 4nm Process Generation, Full Foundry Roadmap", www.tomshardware.com

- Cutress, Ian. "Samsung Announces 3nm GAA MBCFET PDK, Version 0.1". www.anandtech.com.

- Cutress, Dr Ian. "Intel's Manufacturing Roadmap from 2019 to 2029: Back Porting, 7nm, 5nm, 3nm, 2nm, and 1.4 nm". www.anandtech.com.

- Broekhuijsen 2020-01-03T16:28:57Z, Niels. "Samsung Prototypes First Ever 3nm GAAFET Semiconductor". Tom's Hardware. Retrieved 10 February 2020.

- Shilov, Anton. "TSMC: 3nm EUV Development Progress Going Well, Early Customers Engaged". www.anandtech.com.

- Frumusanu, Andrei. "TSMC Details 3nm Process Technology: Full Node Scaling for 2H22 Volume Production". www.anandtech.com.

- "TSMC Dishes on 5nm and 3nm Process Nodes, Introduces 3DFabric Tech | Tom's Hardware". www.tomshardware.com.

- INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS 2017 EDITION - EXECUTIVE SUMMARY (PDF), ITRS, 2017, Table ES2, p.18

- INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS 2017 EDITION - MORE MOORE (PDF), ITRS, 2017, archived from the original (PDF) on 25 October 2018, retrieved 18 April 2019

- Merritt, Rick (19 May 2017), "4 Views of the Silicon Roadmap - Distant hope for a 14-angstrom node", www.eetimes.com

- Patterson, Alan (12 September 2018), "TSMC: Chip Scaling Could Accelerate", www.eetimes.com

- Merritt, Rick (4 March 2019), "SPIE Conference Predicts Bumpy Chip Roadmap", www.eetasia.com

- Zafar, Ramish (12 June 2019). "TSMC To Commence 2nm Research In Hsinchu, Taiwan Claims Report".

- "TSMC has achieved a breakthrough in 2nm, will adopt GAA technology and put it into production in 2023-2024". 13 July 2020.

Further reading

- Lapedus, Mark (21 June 2018), "Big Trouble At 3nm", semiengineering.com

- Bae, Geumjong; Bae, D.-I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; Oikawa, K.; Masuoka, S.; Chun, K.Y.; Park, S.H.; Shin, H.J.; Kim, J.C.; Bhuwalka, K.K.; Kim, D.H.; Kim, W.J.; Yoo, J.; Jeon, H.Y.; Yang, M.S.; Chung, S.-J.; Kim, D.; Ham, B.H.; Park, K.J.; Kim, W.D.; Park, S.H.; Song, G.; et al. (December 2018), "3nm GAA Technology featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications", 2018 IEEE International Electron Devices Meeting (IEDM) (conference paper), pp. 28.7.1–28.7.4, doi:10.1109/IEDM.2018.8614629, ISBN 978-1-7281-1987-8

| Preceded by 5 nm (FinFET) |

MOSFET semiconductor device fabrication process | Succeeded by 2 nm (GAAFET) |