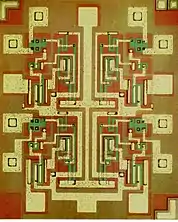

600 nm process

The 600 nm process refers to the level of CMOS (MOSFET) semiconductor fabrication process technology that was commercialized around the 1990–1995 timeframe, by leading semiconductor companies like Mitsubishi Electric, Toshiba, NEC, Intel and IBM.

| Semiconductor device fabrication |

|---|

|

|

(process nodes) |

History

A MOSFET device with a 500 nm NMOS channel length was fabricated by a research team led by Robert H. Dennard, Hwa-Nien Yu and F.H. Gaensslen at the IBM T.J. Watson Research Center in 1974.[1] A CMOS device with a 500 nm NMOS channel length and 900 nm PMOS channel length was fabricated by Tsuneo Mano, J. Yamada, Junichi Inoue and S. Nakajima at Nippon Telegraph and Telephone (NTT) in 1983.[2][3]

A CMOS device with 500 nm channel length was fabricated by an IBM T.J. Watson Research Center team led by Hussein I. Hanafi and Robert H. Dennard in 1987.[4] Commercial 600 nm CMOS memory chips were manufactured by Mitsubishi Electric, Toshiba and NEC in 1989.[5]

Products featuring 0.6 μm manufacturing process

- Mitsubishi Electric, Toshiba and NEC introduced 16 Mbit DRAM memory chips manufactured with a 600 nm process in 1989.[5]

- NEC introduced a 16 Mbit EPROM memory chip manufactured with this process in 1990.[5]

- Mitsubishi introduced a 16 Mbit flash memory chip manufactured with this process in 1991.[5]

- Intel 80486DX4 CPU launched in 1994 was manufactured using this process.

- IBM/Motorola PowerPC 601, the first PowerPC chip, was produced in 0.6 μm.

- Intel Pentium CPUs at 75 MHz, 90 MHz and 100 MHz were also manufactured using this process.

References

- Dennard, Robert H.; Yu, Hwa-Nien; Gaensslen, F. H.; Rideout, V. L.; Bassous, E.; LeBlanc, A. R. (October 1974). "Design of ion-implanted MOSFET's with very small physical dimensions" (PDF). IEEE Journal of Solid-State Circuits. 9 (5): 256–268. Bibcode:1974IJSSC...9..256D. CiteSeerX 10.1.1.334.2417. doi:10.1109/JSSC.1974.1050511. S2CID 283984.

- Gealow, Jeffrey Carl (10 August 1990). "Impact of Processing Technology on DRAM Sense Amplifier Design" (PDF). CORE. Massachusetts Institute of Technology. pp. 149–166. Retrieved 25 June 2019.

- Mano, Tsuneo; Yamada, J.; Inoue, Junichi; Nakajima, S. (1983). "Submicron VLSI memory circuits". 1983 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. XXVI: 234–235. doi:10.1109/ISSCC.1983.1156549. S2CID 42018248.

- Hanafi, Hussein I.; Dennard, Robert H.; Haddad, Nadim F.; Taur, Yuan; Sun, J. Y. C.; Rodriguez, M. D. (September 1987). "0.5 μm CMOS Device Design and Characterization". ESSDERC '87: 17th European Solid State Device Research Conference: 91–94.

- "Memory". STOL (Semiconductor Technology Online). Retrieved 25 June 2019.

| Preceded by 800 nm |

CMOS manufacturing processes | Succeeded by 350 nm |